# An Applications Approach to Benchmarking and Performance Modelling Low Latency Interconnection Networks

by

## Dean Gordon Chester

A thesis submitted to The University of Warwick in partial fulfilment of the requirements  $\qquad \qquad \text{for admission to the degree of}$

**Doctor of Philosophy**

## Department of Computer Science

The University of Warwick

October 2021

# Copyright

© British Crown Owned Copyright 2021/AWE. Published with permission of the Controller of Her Britannic Majesty's Stationery Office. This document is of United Kingdom origin and contains proprietary information which is the property of the Secretary of State for Defence. It is furnished in confidence and may not be copied, used or disclosed in whole or in part without prior written consent of Defence Intellectual Property Rights DGDCDIPR-PL—Ministry of Defence, Abbey Wood, Bristol, BS34 8JH, England.

# Contents

| Li           | st of | Figures                         | vii                    |

|--------------|-------|---------------------------------|------------------------|

| Li           | st of | $\Gamma_{ m ables}$             | viii                   |

| Li           | st of | Listings                        | ix                     |

| A            | ckno  | rledgements                     | x                      |

| D            | eclar | tions                           | xi                     |

| $\mathbf{A}$ | bstra | et .                            | xii                    |

| D            | edica | ion                             | xiii                   |

| Sp           | onso  | rship and Grants                | xiv                    |

| $\mathbf{A}$ | bbre  | iations                         | $\mathbf{x}\mathbf{v}$ |

| 1            | Inti  | oduction                        | 1                      |

|              | 1.1   | Motivations                     | 3                      |

|              | 1.2   | Contributions                   | 5                      |

|              | 1.3   | Thesis Structure                | 6                      |

| 2            | Bac   | ground                          | 8                      |

|              | 2.1   | Parallelisation                 | 8                      |

|              |       | 2.1.1 Speedup                   | 8                      |

|              |       | 2.1.2 Flynn's Taxonomy          | 9                      |

|              |       | 2.1.3 Types of Parallelism      | 11                     |

|              | 2.2   | Performance Engineering         | 13                     |

|              |       | 2.2.1 Benchmarking              | 13                     |

|              |       | 2.2.2 Performance Prediction    | 16                     |

|              | 2.3   | Low Latency Interconnect Design | 20                     |

|              |       | 2.3.1 Communication Stack       | 20                     |

|              |       | 2.3.2 Network Architecture      | 21                     |

|              | 2.4   | Summary                         | 28                     |

| 3            | Cor   | pute Platforms and Applications | 29                     |

|              | 3.1   | Compute Platforms               | 29                     |

|              |       | 3.1.1 Tinis                     | 30                     |

|              |       | 3.1.2 Orac                      | 21                     |

|   |            | 3.1.3 Isambard                                        | 31       |

|---|------------|-------------------------------------------------------|----------|

|   |            | 3.1.4 Cori                                            | 32       |

|   |            | 3.1.5 Astra                                           | 32       |

|   | 3.2        | Applications                                          | 33       |

|   |            | 3.2.1 TeaLeaf                                         | 34       |

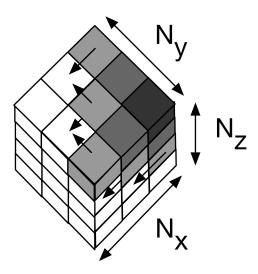

|   |            | 3.2.2 Sweep3D                                         | 35       |

|   | 3.3        | Communication Patterns                                | 36       |

|   |            | 3.3.1 Halo Exchange                                   | 37       |

|   |            | 3.3.2 Reduction                                       | 38       |

|   |            | 3.3.3 Wavefront                                       | 39       |

|   | 3.4        | Summary                                               | 39       |

| 4 | Des        | sign and Implementation of a modern network benchmark | 41       |

| • | 4.1        |                                                       | 42       |

|   |            | 9                                                     | 44       |

|   | 4.2        |                                                       | 47       |

|   |            |                                                       | 52       |

|   | 4.3        |                                                       | 56       |

|   |            |                                                       | 56       |

|   |            | *                                                     | 60       |

|   | 4.4        |                                                       | 63       |

|   |            |                                                       |          |

| 5 |            |                                                       | 65       |

|   | 5.1        |                                                       | 66       |

|   |            |                                                       | 67       |

|   |            |                                                       | 68       |

|   |            | ·                                                     | 68       |

|   |            |                                                       | 69<br>70 |

|   | <b>5</b> 0 |                                                       | 70       |

|   | 5.2        |                                                       | 72       |

|   |            | ~                                                     | 73       |

|   |            | 0                                                     | 74       |

|   | E 9        | 9                                                     | 83       |

|   | 5.3        |                                                       | 87<br>80 |

|   |            |                                                       | 89       |

|   | F 4        | · ·                                                   | 93       |

|   | 5.4        | Summary                                               | 95       |

| 6            | Con  | tention Aware Performance Modelling       | .00 |

|--------------|------|-------------------------------------------|-----|

|              | 6.1  | Network Tapering                          | 101 |

|              |      | 6.1.1 Entire System                       | 103 |

|              |      | 6.1.2 Contended Applications              | 104 |

|              | 6.2  | Network Utilization                       | 105 |

|              | 6.3  | StressBench as simulation validation tool | 110 |

|              | 6.4  | Summary                                   | 111 |

| 7            | Disc | cussions and Conclusions 1                | .15 |

|              | 7.1  | Limitations                               | 116 |

|              |      | 7.1.1 Software                            | 116 |

|              |      | 7.1.2 Hardware                            | 117 |

|              | 7.2  | Future Work                               | 117 |

|              |      | 7.2.1 Benchmarking                        | 118 |

|              |      | 7.2.2 Modelling                           | 120 |

| $\mathbf{A}$ | App  | olications inside of StressBench 1        | .35 |

|              | A.1  | TeaLeaf Motif Implementation              | 135 |

|              | A.2  | TeaLeaf Settings Structure                | 137 |

# List of Figures

| 1.1  | Interacting Applications in relation to time                      | 3  |

|------|-------------------------------------------------------------------|----|

| 2.1  | Flynn's Taxonomy, D represents Data, P is the Processing Ele-     |    |

|      | ments and I is the instruction                                    | 10 |

| 2.2  | Representativeness and Simplicity of Applications Scale           | 14 |

| 2.3  | Distributed Application Communication Stack                       | 20 |

| 2.4  | Network Architecture                                              | 21 |

| 2.5  | Switch Architecture                                               | 22 |

| 2.6  | Fat-Tree Topology                                                 | 23 |

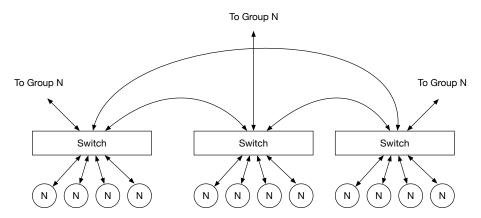

| 2.7  | Dragonfly Topology - Group All-To-All                             | 24 |

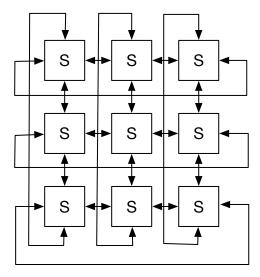

| 2.8  | Torus Topology, S is a Switch in which multiple nodes can reside  | 24 |

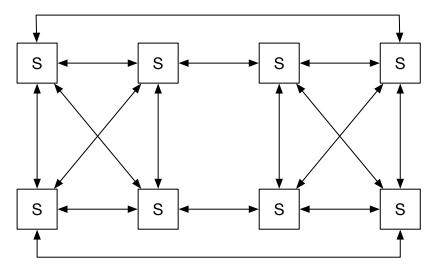

| 2.9  | HyperX Topology, S is a Switch in which multiple nodes can reside | 25 |

| 3.1  | Three Dimensional Wavefront Decomposition                         | 36 |

| 3.2  | Halo Exchange                                                     | 37 |

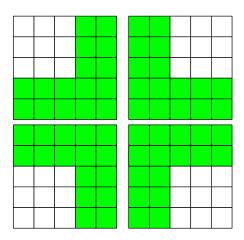

| 3.3  | Reduction - Binary Tree Example                                   | 39 |

| 4.1  | StressBench Architecture                                          | 44 |

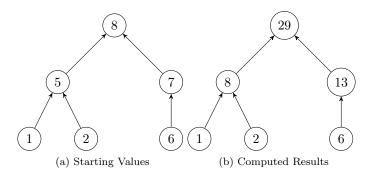

| 4.2  | PingPong Comparisons for Three Machines                           | 48 |

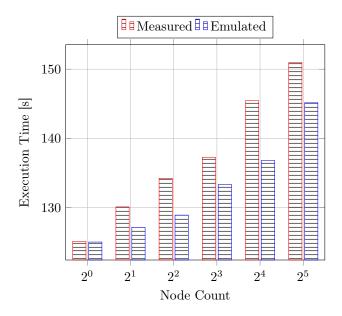

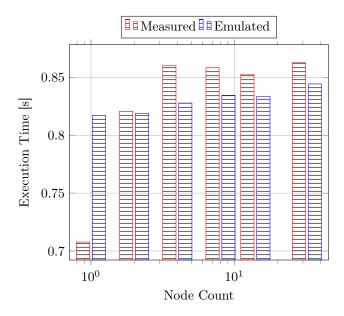

| 4.3  | TeaLeaf Runtime Validation                                        | 50 |

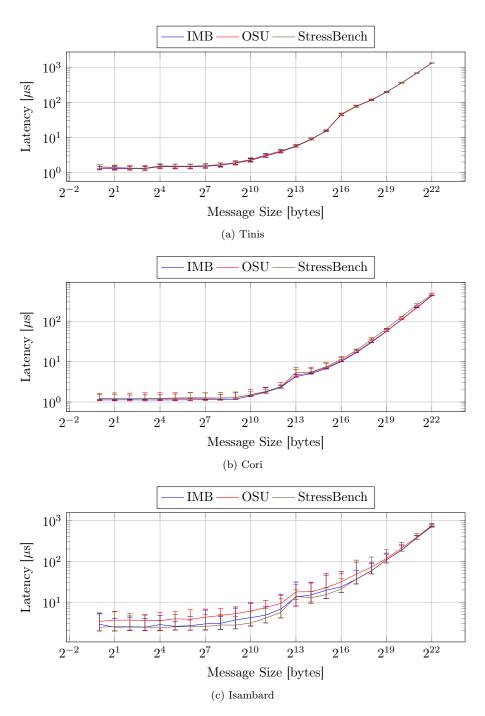

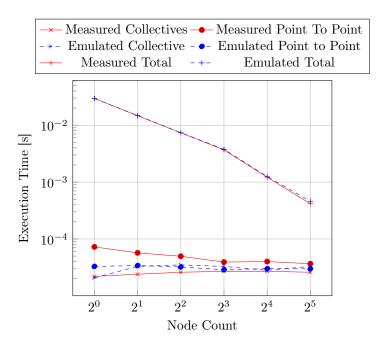

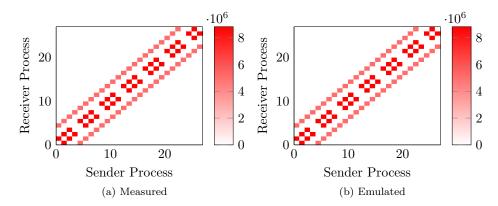

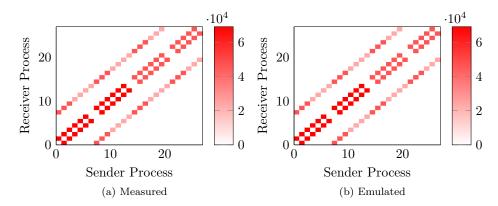

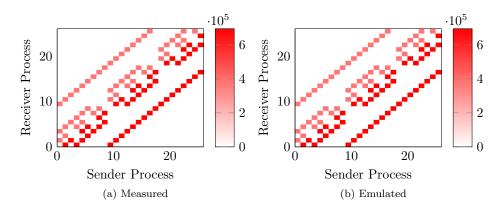

| 4.4  | Measured and Emulated Communication Pattern for Halo2D $$         | 51 |

| 4.5  | Sweep Runtime Validation                                          | 51 |

| 4.6  | Measured and Emulated Communication Pattern for Sweep3D $$ .      | 52 |

| 4.7  | LULESH Runtime Validation                                         | 52 |

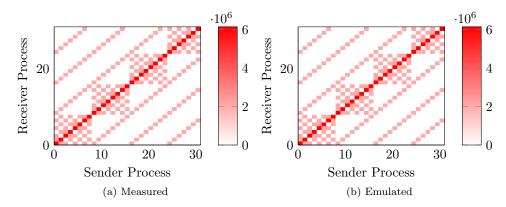

| 4.8  | Measured and Emulated Communication Pattern for LULESH $$ .       | 53 |

| 4.9  | Measured and Emulated Communication Pattern for SWFFT $$          | 53 |

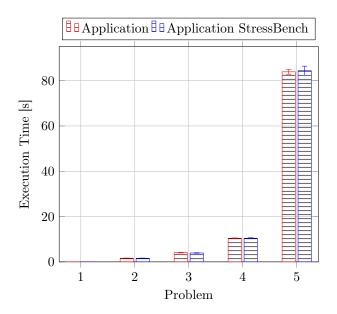

| 4.10 | TeaLeaf Application Problem Sizes                                 | 55 |

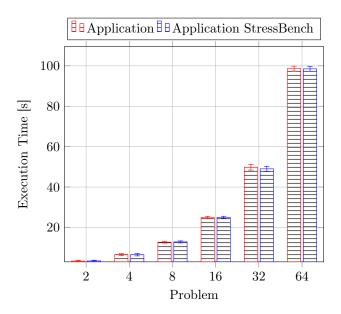

| 4.11 | CloverLeaf Application Problem Sizes                              | 56 |

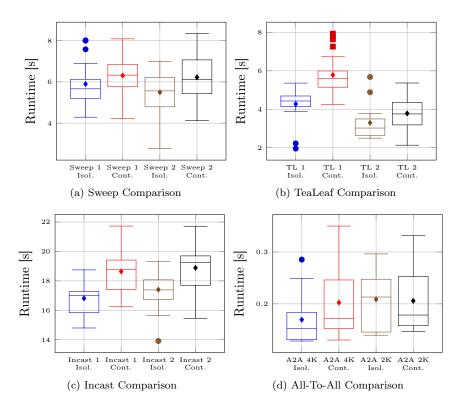

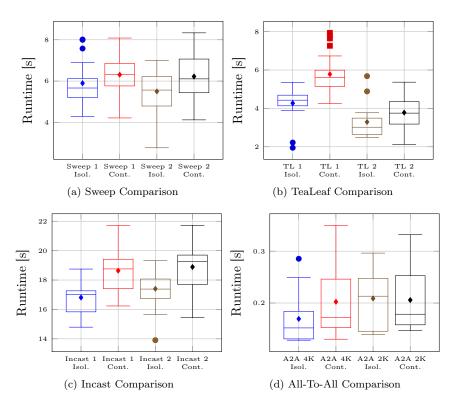

| 4.12 | Application Runtimes in Isolation and in Contention on Tinis      | 59 |

| 4.13 | Application Runtimes in Isolation and in Contention on Isambard   | 60 |

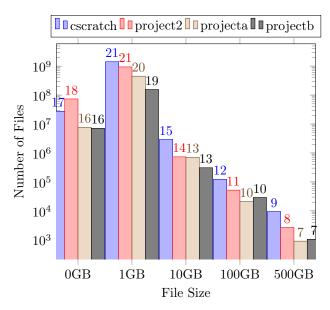

| 4.14 | Measured File Sizes From Four Production Storage Systems          | 61 |

| 4.15 | Job Placement, Diagonal and Hash lines represent different ap-    |    |

|      | plications                                                        | 62 |

| 5.1  | Network Simulation Stack                                          | 66 |

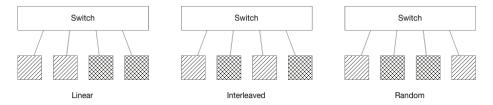

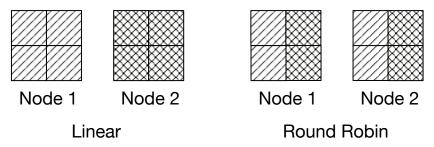

| 5.2  | SST Partitioning Schemes                                          | 71 |

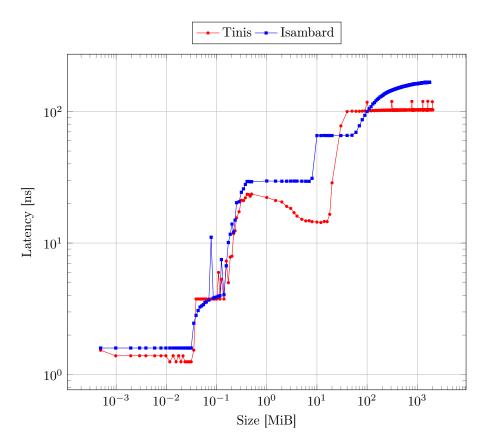

| 5.3  | Measured Memory Latency for Tinis and Isambard                    | 75 |

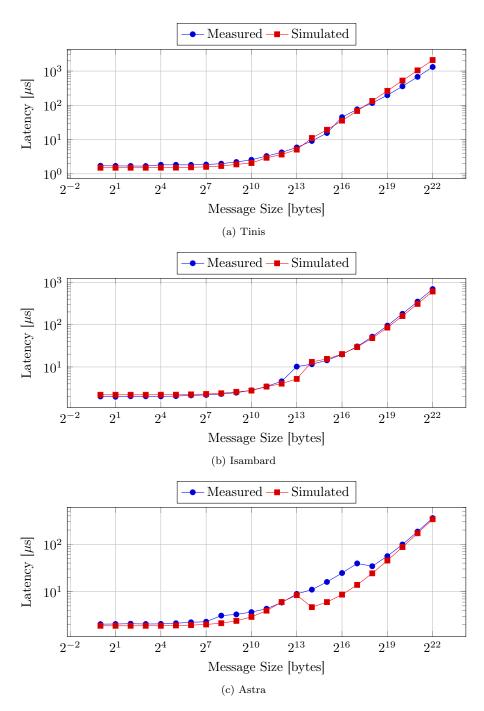

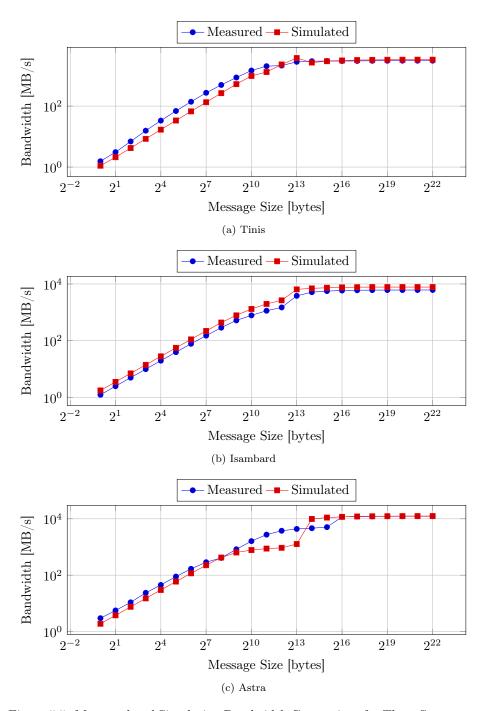

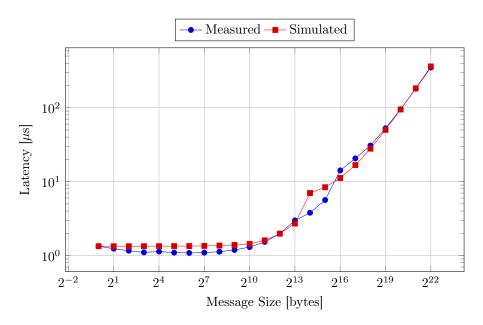

| 5 4  | Measured and Simulation PingPong Comparison for Three Systems     | 77 |

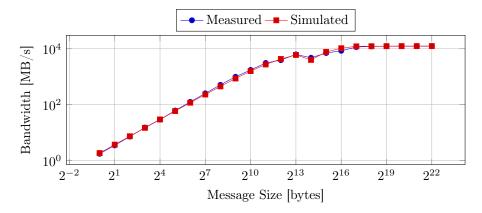

| 5.5  | Measured and Simulation Bandwidth Comparison for Three Sys-                                 |     |

|------|---------------------------------------------------------------------------------------------|-----|

|      | tems                                                                                        | 79  |

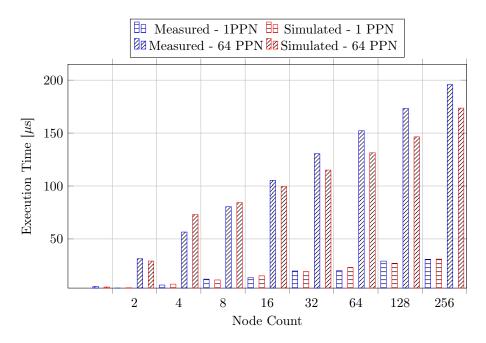

| 5.6  | $\label{thm:measured} \mbox{Measured and Simulated AllReduce Operation Comparison - Isam-}$ |     |

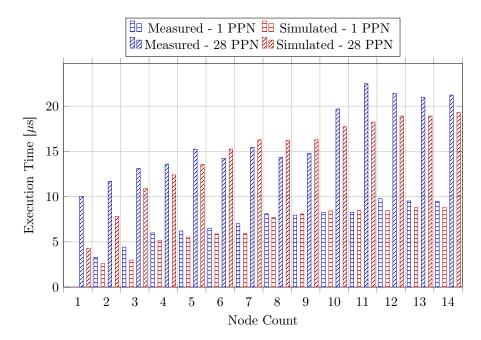

|      | bard                                                                                        | 80  |

| 5.7  | Measured and Simulated AllReduce Operation Comparison - Ti-                                 |     |

|      | nis 16 PPN                                                                                  | 80  |

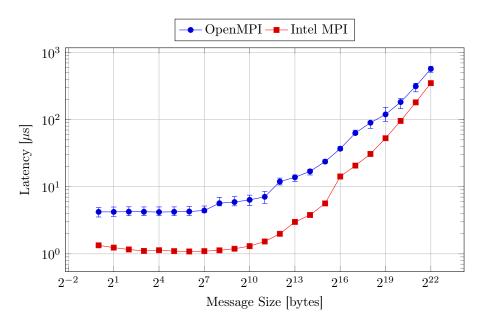

| 5.8  | Orac MPI Latency - OpenMPI vs Intel MPI                                                     | 81  |

| 5.9  | Orac Latency Simulation vs Measured (Intel MPI)                                             | 82  |

| 5.10 | Orac Bandwidth Simulation vs Measured (Intel MPI)                                           | 82  |

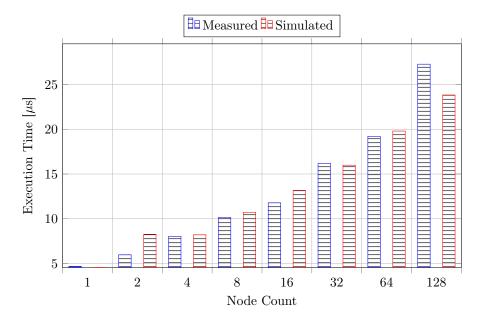

| 5.11 | Measured and Simulated All<br>Reduce Operation Comparison - Orac                            | 83  |

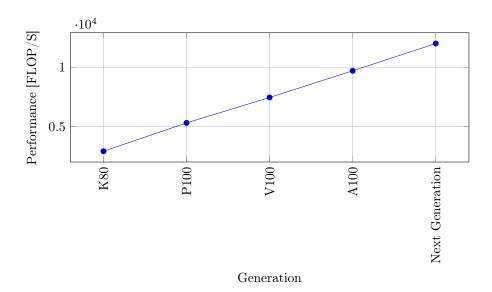

| 5.12 | GPU Performance Trend                                                                       | 89  |

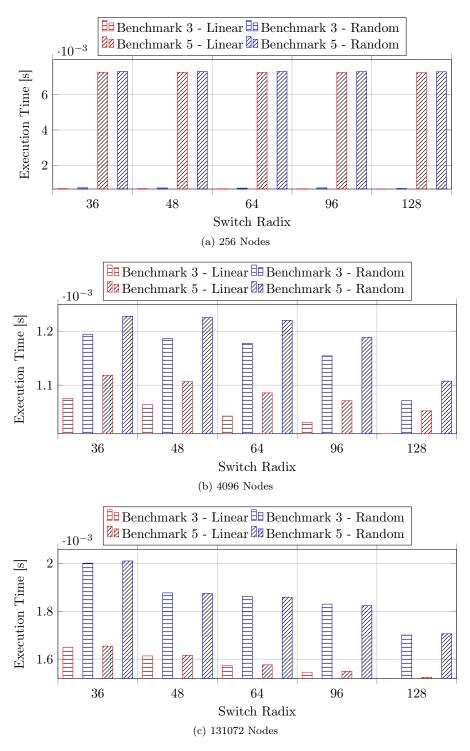

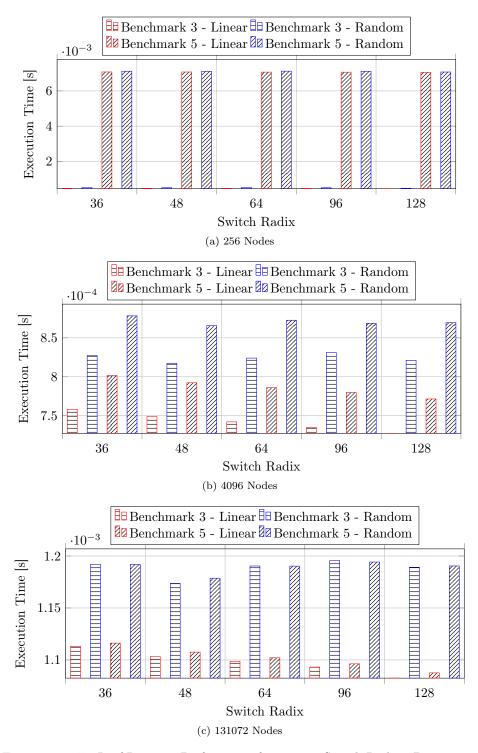

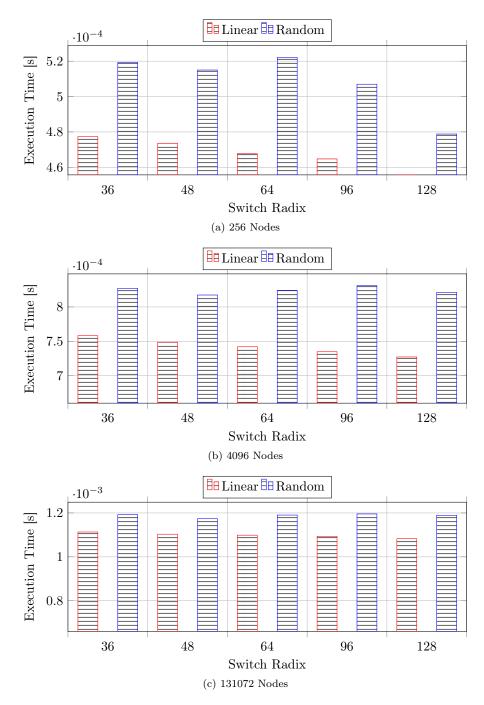

| 5.13 | ${\it TeaLeaf Runtime Performance for varying Switch \ Radix - Fat \ Tree}$                 | 91  |

| 5.14 | Sweep3D Runtime Performance for varying Switch Radix - Fat                                  |     |

|      | Tree                                                                                        | 92  |

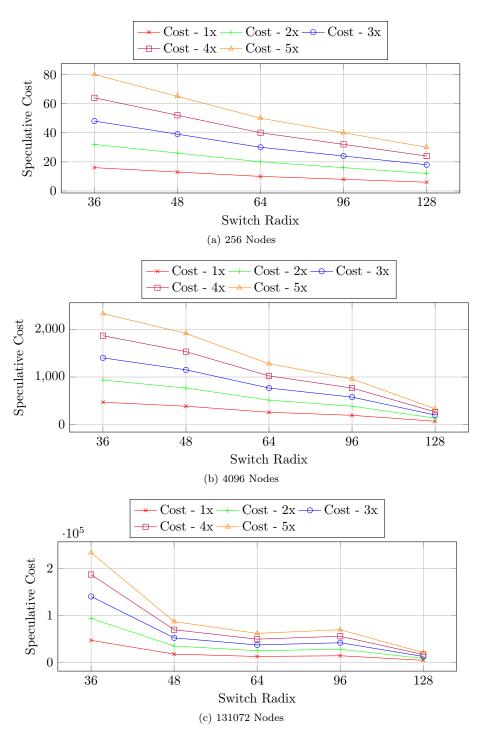

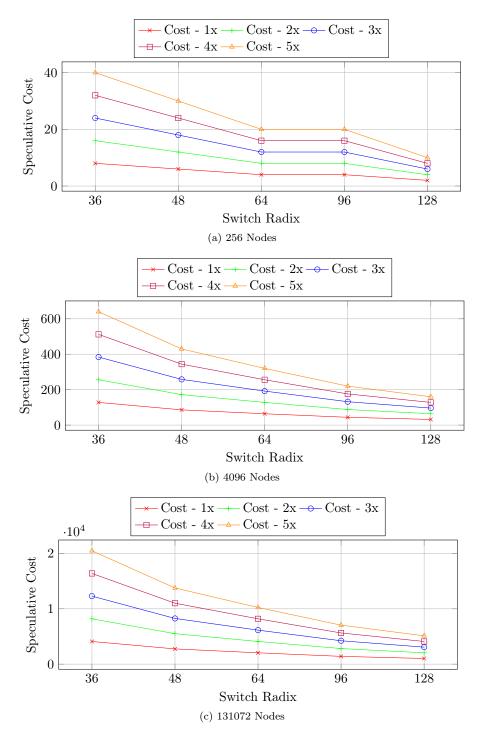

| 5.15 | Costs Trends for Fat Tree Network                                                           | 94  |

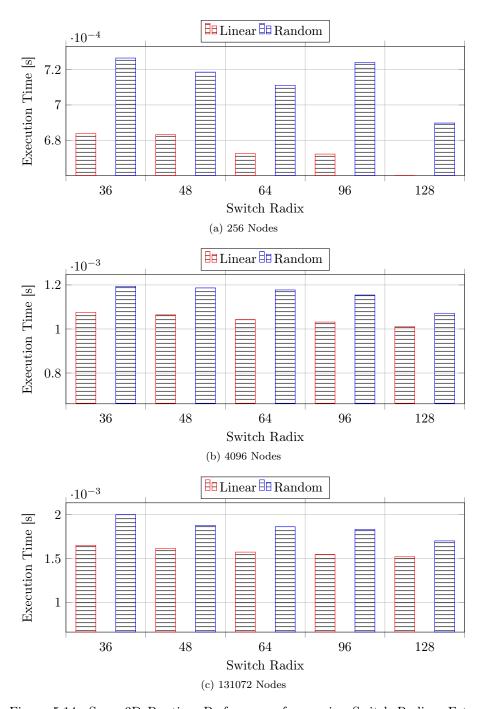

| 5.16 | ${\it TeaLeaf Runtime Performance for varying Switch \ Radix - Dragonfly}$                  | 97  |

| 5.17 | Sweep3D Runtime Performance for varying Switch Radix - Drag-                                |     |

|      | onfly                                                                                       | 98  |

| 5.18 | Costs Trends for Dragonfly Network                                                          | 99  |

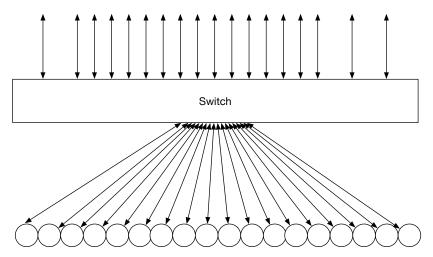

| 6.1  | Non-Blocking Leaf Switch - Nodes represented by circles 1                                   | .02 |

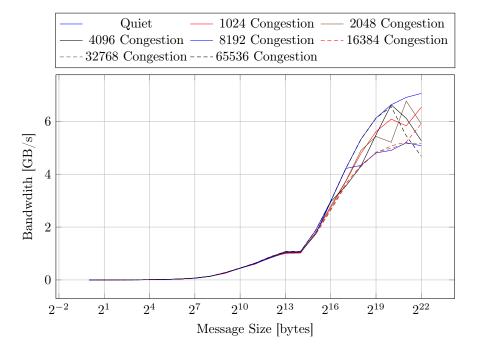

| 6.2  | Simulated Bandwidth with varying congestion size                                            | .06 |

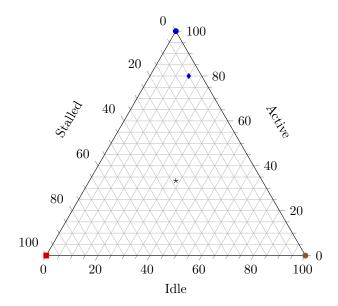

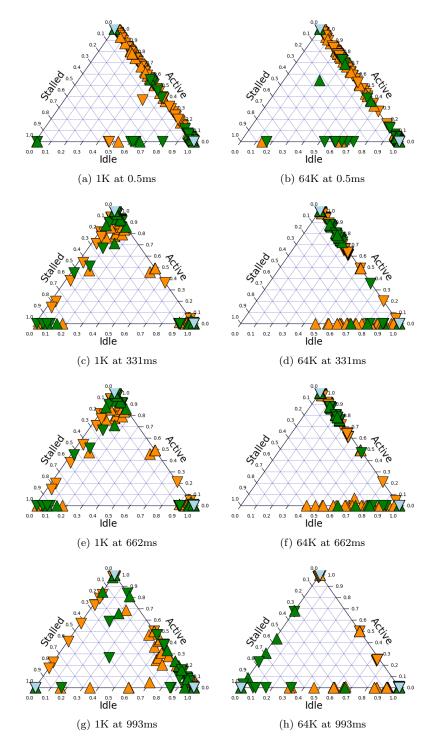

| 6.3  | Example Ternary Plot                                                                        | .08 |

| 6.4  | Congestor Ternary Plot for 1K and 64K congestors, orange repre-                             |     |

|      | sent NIC ports, Green represent the level 1 ports, blue represents                          |     |

|      | the core switch ports. The direction of the triangle shows whether                          |     |

|      | it is an uplink or downlink                                                                 | 13  |

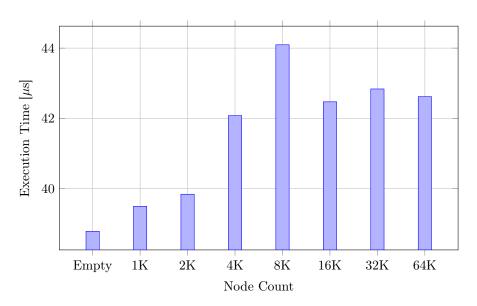

| 6.5  | AllReduce Times against AllToAll Congestor Size                                             | 14  |

|      |                                                                                             |     |

# List of Tables

| 3.1 | Tinis Specification                                                                                                  |

|-----|----------------------------------------------------------------------------------------------------------------------|

| 3.2 | Orac Specification                                                                                                   |

| 3.3 | Isambard Specification                                                                                               |

| 3.4 | Cori Haswell (HSW) Specification                                                                                     |

| 3.5 | Cori Knights Landing (KNL) Specification                                                                             |

| 3.6 | Astra Specification                                                                                                  |

| 4.1 | SWFFT Runtime Validation                                                                                             |

| 4.2 | Comparison of CI for Incast and File I/O for Applications $$ 60                                                      |

| 4.3 | Comparison of Application Workload against Congestion Impact                                                         |

|     | - Tinis                                                                                                              |

| 4.4 | Comparison of Application Workload against Congestion Impact                                                         |

|     | - Isambard                                                                                                           |

| 5.1 | TeaLeaf Benchmark 3 - Model Validation                                                                               |

| 5.2 | TeaLeaf Benchmark 5                                                                                                  |

| 5.3 | Sweep3D Weak Scale - $50 \text{x} 50 \text{x} 800$ Per Process - Astra $\ \ldots \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $ |

| 5.4 | Sweep3D Weak Scale - $50 \text{x} 50 \text{x} 800$ Per Process - Isambard 88                                         |

| 5.5 | Fat Tree Network Configurations                                                                                      |

| 5.6 | Fat Tree Switch Count Per Switch Radix                                                                               |

| 5.7 | Dragonfly Network Configurations                                                                                     |

| 6.1 | Network Tapers                                                                                                       |

| 6.2 | Network Tapering for Linear Job Placement                                                                            |

| 6.3 | Network Tapering for Random Job Placement                                                                            |

| 6.4 | Isolated Runtimes for Tapered Fat Tree                                                                               |

| 6.5 | Network Tapering on multiple applications - Linear Job Placement $105$                                               |

| 6.6 | Network Tapering on multiple applications - Random Job Place-                                                        |

|     | ment                                                                                                                 |

| 6.7 | Comparison of CI for Incast Traffic for Tinis                                                                        |

| 7.1 | Comparison of Applications against Congestion Impact - Isambard 118                                                  |

# Listings

| 2.1  | OpenMP Example                                                           |

|------|--------------------------------------------------------------------------|

| 3.1  | Example 2D Halo Exchange                                                 |

| 3.2  | Example Octant Sweep                                                     |

| 4.1  | Example Input                                                            |

| 4.2  | StressBench Input for TeaLeaf                                            |

| 5.1  | MPI Call                                                                 |

| 5.3  | Hermes Latency Parameters                                                |

| 5.4  | Transmit Copy Send Parameters for FireFly                                |

| 5.5  | Topology Parameters for Cray Aries                                       |

| 5.6  | Isambard Memory Parameters                                               |

| 5.7  | Tea<br>Leaf Performance Model Input for Benchmark 3 128 Nodes $$ . $$ 84 |

| 5.8  | Exit Early Condition for Sweep3D Motif                                   |

| 5.9  | Angle Blocking for Sweep3D Motif                                         |

| 5.10 | TeaLeaf Halo Exchange Y Direction Motif                                  |

| 6.1  | Contended Network Utilisation SST Input Workload 109 $$                  |

| 7.1  | Proposed Parameter Extension to StressBench                              |

| A.1  | TeaLeaf Motif                                                            |

| A.2  | Modified Settings Structure                                              |

I would like to thank my supervisors, Prof. Stephen Jarvis, Dr. Suhaib Fahmy and Dr. Gihan Mudalige for their support and in depth discussions that have shaped this work over the past four years. Their encouragement to develop as a scientist and continue to explore and push ideas and concepts has been an invaluable experience.

I would also like to thank Dr. Simon Hammond at Sandia National Laboratories for his continued support and mentorship throughout the project; without his guidance this project would not be where it is today. Additional thanks go to Dr. Taylor Groves at the National Energy Research Scientific Computing Center for discussions around network congestion and other types of distributed applications away from multi-physics.

I would also like to thank my past and present colleagues and friends in the High Performance Scientific Computing Group: Dr. Steven Wright, Dr. James Davies, Dr. James Dickson, Dr. Dominic Brown, Dr. Richard Kirk, Dr. Andrew Owenson, Andrew Lamzed-Short, Alex Cooper, Archie Powell and Kabir Choudry for making the office environment an enjoyable place to work and study. Special thanks to Dom and Richard for having been there since the start and through the entire journey from the frustration to the laughter which encouraged me to improve and continue.

From the Department of Computer Science I wish to thank Maria Ferriero, Emma Woollacott, Sharon Howard, Dr. Roger Packwood, Paul Williamson, Richard Cunningham and the rest of the secretarial and technical staff for their assistance around administration, technical support throughout my Ph.D allowing me to focus on research.

To the staff from AWE who have gone above and beyond to aid my research, thank you Dr. Timothy Law, Dr. Seimon Powell and Prof. Richard Smedley-Stevenson.

Dr. Matt Ismail and Dr. Dugan Witherick based at the Scientific Computing Research Technology Platform, thank you for your patience and assistance with providing access to computing resources to facilitate my research.

To my family and friends, Mum, Dad, Dr. Adam Chester, Tara, Hope, Louise, Ben, Dr. John Galvin, William, Linda, Auntie Penny, Uncle Dave, Paul Fellows, Simon Cooper, Dr. Simon Fowler, Dan Prince, Dr. Peter Butcher, Joe Frangoudes, Noah Hall, Helen McKay and James Van Hinsbergh thank you for the help and support over the last four years, I would have not been able to have done this without your support. I would lastly like to thank my partner Fiona for her love and support.

This thesis is submitted to the University of Warwick in support of my application for the degree of Doctor of Philosophy. It has been composed by myself and has not been submitted in any previous application for any degree. The work presented (including data generated and data analysis) was carried out by the author except in the cases outlined below:

- The simulator presented in Chapter 5 was developed at Sandia National Laboratories as a collaborative effort between the Department of Energy (DOE), Industry and Academia. Some of the work outlined in this thesis has contributed to the development, testing and validation of this simulator.

- Measured data from Astra was collected by Dr. Simon D Hammond.

- Measured data from Cori was collected by Dr. Taylor L Groves.

- Figure 4.1 was created by Dr. Steven A Wright.

- Inode Sizes from Cori's Storage Systems were collected by Dr. Lisa Gerhardt, Kirill Lozinskiy and Ravi Cheema (data for Figure 4.14).

Parts of this thesis have been published by the author:

- [35] D. G. Chester, S. A. Wright, and S. A. Jarvis. Understanding communication patterns in HPCG. Electronic Notes in Theoretical Computer Science, 340:55–65, 2018

- [34] D. G. Chester, S. A. Wright, S. D. Hammond, T. R. Law, R. P. Smedley-Stevenson, S. Maheswaran, and S. A. Jarvis. Full-system modeling and simulation: contributions towards coupling, contention, and I/O. In MOD-SIM 2019, 2019

- [32] D. G. Chester, T. L. Groves, S. D. Hammond, T. R. Law, S. A. Wright, R. P. Smedley-Stevenson, S. A. Fahmy, G. R. Mudalige, and S. A. Jarvis. StressBench: A Configurable Full System Network and I/O Benchmark Framework. In *Proceedings of ISC HIGH PERFORMANCE 2021*, 2021

- [33] D. G. Chester, T. L. Groves, S. D. Hammond, T. R. Law, S. A. Wright, R. P. Smedley-Stevenson, S. A. Fahmy, G. R. Mudalige, and S. A. Jarvis. StressBench: A Configurable Full System Network and I/O Benchmark Framework. In 2021 IEEE High Performance Extreme Computing Conference (HPEC), 2021 (Awarded Best Paper)

### **Abstract**

As the field of High Performance Computing (HPC) approaches the Exascale era we see larger systems coming online with a rich set of applications and programming paradigms given the diverse system architecture employed to deliver petascale levels of performance. Underpinning these distributed applications is the use of interconnected nodes; something which can contribute to significant performance degradation when a machine is highly utilised.

This thesis examines the interactions between communication patterns commonly seen in distributed applications written on top of Message Passing Interface (MPI), with a benchmark framework (StressBench) designed to orchestrate concurrent communication patterns. Application replay through StressBench yields reproducible applications with in 15% difference in runtime, showing that it provides a useful; abstraction from commercially sensitive production applications. A congested workload is distributed across two supercomputers demonstrating a slow down for application and Input Output (I/O) traffic, and the effects of job placement on I/O and application traffic is investigated with the benchmark framework.

This thesis documents a validation methodology for a layered simulator built on top of Structural Simulation Toolkit (SST). Using the validated hardware platforms accurate performance models are developed for four systems, and two applications on top of the SST which are then used to evaluate future network designs, both to support the development of next generation interconnection networks and design responses for an Request for Proposal (RFP).

This thesis is dedicated to my Grandfather. William 'Bill' Chester (1934-2018)

# Sponsorship and Grants

The research presented in this thesis was made possible by the support of the following benefactors and sources:

• Joint AWE-Warwick University: Centre for Computational Physics (CCPP) (Grant Number: 30411884)

### Abbreviations

ACK Acknowledgement

API Application Programming Interface

ASIC Application Specific Integrated Circuit

AWE Atomic Weapons Establishment

**BDW** Broadwell

**BM** Benchmark

**BSP** Bulk Synchronous Parallel

CFD Computational Fluid Dynamics

CG Conjugate Gradient

CPU Central Processing Unit

**DOE** Department of Energy

GPFS General Parallel File System

GPU Graphics Processing Unit

$\mathbf{FFT}$  Fast Fourier Transform

${f FLOP/s}$  Floating-Point Operations Per Second

**HPC** High Performance Computing

**HPCG** High Performance Conjugate Gradients

I/O Input Output

IPL Instruction-Level Parallelism

$\mathbf{IQR}$  Inter-Quartile Range

ITAC Intel Trace Analyzer and Collector

$\mathbf{HSW}$  Haswell

KNL Knights Landing

LAN Local Area Network

**OFI** OpenFabrics Interfaces

OSI Open Systems Interconnection

OSU Ohio State University

MIMD Multiple Instruction Multiple Data

MPI Message Passing Interface

MISD Multiple Instruction Single Data

NACK Negative Acknowledgement

NERSC National Energy Research Scientific Computing Center

NIC Network Interface Controller

PGAS Partitioned Global Address Space

PMIx Process Management Interface - Exascale

**QoS** Quality of Service

RFP Request for Proposal

SAI Stalled, Active, Idle

SDLC Systems Development Life Cycle

SHMEM Symmetric Hierarchical Memory

SISD Single Instruction Single Data

SIMD Single Instruction Multiple Data

SPMD Single Program Multiple Data

${f SST}$  Structural Simulation Toolkit

UGAL Universal Globally Adaptive Load-balanced Routing

VC Virtual Channel

# CHAPTER 1

### Introduction

Computation provides a vital method for investigating scientific phenomena that are impractical to physically measure. It proves a safe, reliable and repeatable environment to experiment. Some of these simulations require larger computers to provide the computation resources, called supercomputers. Supercomputers are large machines that support calculating large amounts of computation, typically faster than desktop computers. The research field around design, development and support of these software and hardware systems is called High Performance Computing (HPC).

The Atlas Computer (delivered in 1962) is considered one of the first supercomputers [82], it could perform a floating-point multiplication operation in around 5ms. Modern supercomputers can perform often 10 orders of magnitude more Floating-Point Operations Per Second (FLOP/s) than these systems although they have shaped how HPC has developed. Some current supercomputers are constructed from commodity of-the-shelf hardware and networked with a low latency interconnection network called an interconnect, such as InfiniBand [1] which is commonly used. Previous interconnections networks have come and gone due to more advanced technology developing, one such network is Myrinet [20], originally a 1Gb/s link specifically designed for supercomputers due to it's low latency and high bandwidth, with a 10Gb version being released in 2005. Machines first appeared with this network in 1995 and the last machine appeared on the June 2014 TOP500 list [121]. Custom proprietary networks are also common place inside of supercomputers with IBM (for BlueGene product range<sup>1</sup>) and Cray/HPE developing specialist interconnects for supercomput-

$<sup>^1\</sup>mathrm{See}:\ \mathsf{https://www.ibm.com/common/ssi/ShowDoc.wss?docURL=/common/ssi/rep\_sm/1/877/ENUS0207-_h01/index.html$

ers. The current Cray/HPE offering in the EX series<sup>2</sup> is a 200Gbps network providing low latency but higher jitter compared to an equivalent InfiniBand solution [47]. Newer networks provide advanced routing algorithms which may not provide the minimal path, this could result in higher latencies and decreased network throughput. This increases the time to solution for an application.

Modern distributed HPC applications typically have to exchange data as the problem sizes make them unfeasible to run on a single node, this is because of power, cost and physical size limitations. One approach is to distribute the problem over multiple nodes thereby achieving more physical memory, somewhere in the order of petabytes. This data exchange either between CPU cores (intranode) or nodes (inter-node) is limited by latency and bandwidth of the memory and/or network subsystem. As the next era of supercomputers enters (named the exascale-era) we see restrictions on power requirements with the Department of Energy (DOE) (a large purchaser of supercomputers) stating the first generation of exascale supercomputers should consume 20MW at most [81]. This is unachievable with current hardware configurations. In an effort to satisfy this power requirement we see new node architectures developing which include an accelerator(s) such as a Graphics Processing Unit (GPU). Summit (the second fastest supercomputer as of the June 2021 TOP500 list [123]) features 6 GPUs per node [103].

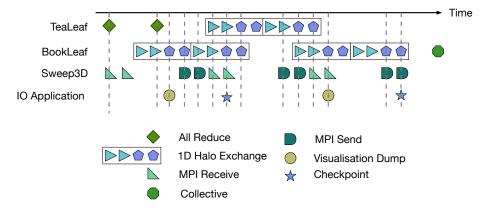

Large supercomputers typically run lots of small jobs rather than one full system job (although this does happen) at one time, these jobs can interfere with each other affecting application runtime and performance [131]. The effects of the inter-job interference is a relatively new field in the HPC research area and is of great interest as this can affect application communication performance by as much as 50% for application communications on highly utilised supercomputers [131]. Figure 1.1 shows how some applications could interfere with each other throughout an application run. The vertical dotted lines highlight the points at which network contention could affect performance and the shapes

$<sup>^2</sup> See: \\ https://support.hpe.com/hpesc/public/docDisplay?docId=a00109703en\_us\&docLocale=en\_US \\$

represent different communication patterns. In reality contending application communication patterns will not lineup as neatly as the abstract figure due to load imbalance and OS jitter, but provides a good visual representation for the problem at hand.

Figure 1.1: Interacting Applications in relation to time

Benchmarking advanced features is widely used to compare and contrast Central Processing Unit (CPU) architectures yet are largely ignored for the networking with current procurement procedures focusing on peak performance numbers to aid decisions, which may not always be attainable in production.

This thesis investigates the benchmarking and modelling modern low latency interconnection networks by focusing on application communication patterns rather than traditional network benchmarks such as latency and bidirectional bandwidth. This work aims to act as a case study for benchmarking and performance modelling activities for future design and procurement processes as the techniques presented in this thesis exercise the advanced networking features that are arising in current and next generation low latency interconnection networks.

### 1.1 Motivations

Compute hardware has improved at a rapid pace of the last few decades resulting in CPUs allowing results to be computed faster although this data movement has become the bottleneck due to memory and Input Output (I/O) subsystem performance not growing at the same rate [93]. Both of these impact the network performance which results in slower time to solutions for applications, as does larger dense nodes seen in recent supercomputers. The memory bottleneck can have a significant performance implications for data transmitted over the network as it limits the network injection rate, to see in advances in more memory bandwidth core counts are growing per socket to deliver performance. The I/O subsystem can impact the network traffic as latency sensitive (small) messages have to contend with the large bandwidth sensitive (large) messages which leads to increases in the time to solution for applications, thus slowing them down.

As network architectures evolve we are seeing the development of adaptive routing algorithms, congestion control and Quality of Service (QoS) effect the end user experience and time to solution for applications because these features try to act more fairly than providing the minimum path, while the minimum path should deliver the best performance, this may not always be the case when a network becomes congested. These issues will only continue to deteriorate as networks grow in size.

Memory performance limits the network injection rate as memory has to be read and injected in to the network when transmitting, and written to memory once received [89, 90, 124]. While recent developments allow the Network Interface Controller (NIC) to interface with the memory directly removing the need to communicate with the CPU the memory bus latency and bandwidth becomes the issue. This can be further impacted by how the memory is managed by an application, in the case of a simple latency benchmark the send/receive buffers could be contiguous memory where as an application may have to stride across the memory accessing non-contiguous blocks, when accessing multi-dimensional arrays [56].

Slow parallel I/O performance means that I/O traffic has to reside inside of the network while waiting to be relayed to the I/O nodes and depending on the network design and job placement could affect the time to solution for applications. While we explicitly state I/O traffic this could be any type of traffic waiting to propagate through a network; typically I/O traffic has to wait for the I/O node to read/write to disk which is slower than system memory. This type of traffic typically is also routed to the same endpoint further increasing chances of network contention.

### 1.2 Contributions

This thesis makes the following contributions:

- We present the design and implementation a new Message Passing Interface (MPI) and I/O Benchmark framework (StressBench) capable of driving and stressing network fabrics based on application workloads. Replicated application workloads of four applications have been validated, with a maximum difference of 15%. A full system workload is replicated to demonstrate application performance degradation due to network and I/O contention across two systems. We demonstrate how StressBench can be used for performance studies investigating the effects of network contention with multiple patterns against I/O traffic.

- We present a validation methodology and validated network models for three common network fabrics built on top of the Structural Simulation Toolkit (SST). These validated network models are used to develop accurate performance models for Sweep3D and TeaLeaf. Using these network models the design space of interconnection networks is explored for potential exascale systems, looking at cost, switch radix and runtime performance.

- Contention aware performance models are constructed to understand the performance degradation due to shared resource contention in the network.

We demonstrate that with a tapered Fat Tree bandwidth can reduced by

as much as 2GB/s when in contention with an 64K AllToAll congestion pattern. StressBench is used to compare the effects of real network performance against the simulated network making use of the full system workload introduced with StressBench.

### 1.3 Thesis Structure

The structure of the thesis is as follows:

- Chapter 2 describes the terminology and techniques used in the High Performance Computing, Benchmarking and Performance Modelling. This chapter also introduces the design of a low latency interconnection network.

- Chapter 3 presents the hardware and software used throughout this thesis.

The three hardware platforms are documented and two applications have been used throughout this thesis Sweep3D and TeaLeaf.

- Chapter 4 documents the design and implementation of StressBench, application replication validation results and two performance studies to understand the effects of network contention on application performance.

- Chapter 5 introduces network simulations with SST, presents the validated network models and performance models for Sweep3D and TeaLeaf, and future network design exploration is explored.

- Chapter 6 outlines contention aware performance modelling and presents contention aware performance models to understand performance degradation through simulation.

- Chapter 7 summaries the research outlined in this thesis.

The work presented in this thesis started from understanding communication patterns in an application [35], the tools and techniques used in that paper have been used throughout this thesis. The work from Chapter 4 has been published

as both a poster [32] and research paper [33] at ISC 2021 and IEEE HPEC respectively. The analysis of network degradation inside of the network switches has been published as a poster [34] at MODSIM 2019.

# CHAPTER 2

## Background

Performance gains can come through two forms, software optimisations or hardware optimisations. For software optimisations ensuring that the hardware is fully utilised in the best way possible. With hardware optimisations ensure that the application is running as fast as the hardware will allow. Both of these optimisations need to be exploited to achieve a high level of performance. This performance is often limited by some underlying theories which are described in this chapter.

This chapter is as follows, Section 2.1 presents some of the underlying laws governing parallelisation. Section 2.2 introduces system engineering concepts and shows the state of the art for benchmarking and performance modelling. Section 2.3 is a primer on network architecture introducing the three key elements in a low latency interconnection network.

### 2.1 Parallelisation

This section covers the laws governing the behaviour and limits of parallel computation and the classifications and types of parallelisms that can be exploited to obtain high levels of performance from parallel applications.

#### 2.1.1 Speedup

Speedup is a measure of scalability for an application, it is the ratio of serial runtime  $(T_s)$  over parallel runtime  $(T_p)$  (see Equation (2.1)). This metric allows for a quick comparison to see how an application is performing as the parallel runtime decreases with more computational resources. If an application

demonstrates a linear speedup then the application scales well.

$$S = \frac{T_s}{T_p} \tag{2.1}$$

G Amdhal et al. proposes that the maximum limit from parallelisation is governed by the time spent performing serial operations (see equation 2.2) [10]. In equation 2.2 s and p refer to the serial and parallel execution times respectively and n is the number of processes the parallel section is spread across.

Speedup =

$$\frac{s+p}{s+\frac{p}{n}}$$

(2.2)

The approach taken by G Amdhal et al. focuses on a varying problem size rather changes in runtimes. Gustafson proposes the following change to calculating speedup as seen in equation 2.3 [62].

$$Speedup = n + (1 - n)s \tag{2.3}$$

This approach focuses on the parts of the application that are typically fixed. This approach is favoured as problem sizes typically grow to match capacity rather than choosing to run the same problem size faster across more resources [62]. This can be considered to demonstrate how well an application weak scales.

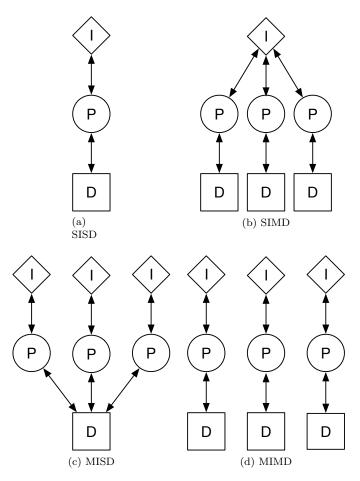

#### 2.1.2 Flynn's Taxonomy

Flynn et al. proposes four types of parallelism for computer architectures [55], Figure 2.1 shows the differences in the four ideas proposed. Single Instruction Single Data (SISD) provides a basic building block of computation, one process operates on a single data block with one instruction. Single Instruction Multiple Data (SIMD) applies the same instruction to multiple blocks of data simultaneously, this is similar to a vector processor or instruction set like Intel SSE or AVX instructions. Multiple Instruction Single Data (MISD) allows for

multiple instructions to operate on the same data allowing for task repetition supporting fault tolerance. This approach is uncommon but one example of a MISD design are the flight control computers of the space shuttle [118]. Multiple Instruction Multiple Data (MIMD) allows for multiple instructions to operate on multiple blocks of data, most of the implementations for MIMD are shared memory based.

Figure 2.1: Flynn's Taxonomy, D represents Data, P is the Processing Elements and I is the instruction

In addition to these classifications there exists another classification, Single Program Multiple Data (SPMD) [45]. This classification has become synonymous with parallel scientific applications, such as MPI based applications.

### 2.1.3 Types of Parallelism

Three types of fundamental parallelism exist, Task Level, Data Level and Instruction Level. If all of these are exploited effectively then an application will perform optimally, but often some of these parallelisms are unable to be exploited together due to loss of accuracy. This is because the order of floating-point operations differ between an single threaded and multi-threaded loop, this can be corrected by ensuring that floating-point operations occur in the correct order.

#### Task Level Parallelism

Task parallelism can take the form of either message passing, or a multi-threaded approaches. There exists a hybrid message passing and multi-threaded approach to ensure resources can be utilised to their fullest, this is useful with certain unstructured applications such as LULESH [74].

Multi-Threading This approach allows communication where memory is located on the same array and can be easily achieved with a variety of libraries, such as PThreads<sup>1</sup> or OpenMP [41]. OpenMP is more common for HPC applications than PThreads.

OpenMP is implemented with the use of compiler directives (called pragmas) and the compiler handles the creation and deletion of the thread. OpenMP uses the fork-join model for thread creation and deletion. At the start of the parallel execution block threads are created and forked and then perform their portion of work; finally joining when the last thread has completed its work [2]. Listing 2.1 shows a simple threaded loop with OpenMP.

```

#pragma omp parallel for

for(int i = 0; i < x; i++)

{

u[i] = u[i] * constant;</pre>

```

<sup>&</sup>lt;sup>1</sup>See: https://man7.org/linux/man-pages/man7/pthreads.7.html

5 }

Listing 2.1: OpenMP Example

One disadvantage of multi-threaded applications is that they must reside on the same node as the data cannot be passed between nodes. This limits the problem size given restrictions on RAM and processing power.

Message Passing Message passing allows inter-node communication to take place so messages can be passed around sharing information between nodes. The MPI standard [57] defines the interface for implementations to provide, this is often abstracted away from the underlying network hardware (see Section 2.3.1).

Several studies have looked at the effect of running message passing for intranode demonstrating that there is a performance impact compared to a shared memory, multi-threaded approach [73, 110].

#### Data Level Parallelism

Vectorisation is a way to make Data Level Parallelism possible and can be represented by SIMD from Flynn's Taxonomy. Vector processors operate on large one-dimensional arrays of data called vectors. These approaches were common in the early days of supercomputers with the Cray-1 being a vector machine [111].

Vector processing units are now commonly built in to generalised CPU architectures with additional instructions such as AVX512 [109].

#### Instruction Level Parallelism

Instruction-Level Parallelism (IPL) shows how many of the operations a computer program the hardware can perform simultaneously. To achieve IPL two techniques could be used, firstly increasing the depth of the instruction pipeline, allows more operations to be overlapped. A second approach is to increase the number of instructions that are run at every stage of the instruction pipeline [106].

### 2.2 Performance Engineering

Performance engineering covers a wide variety of techniques to ensure systems comply to requirements during the Systems Development Life Cycle (SDLC). This section discusses two techniques used throughout the lifetime of a HPC system, benchmarking and modelling. Benchmarking demonstrates that a system can ascertain a level of performance once constructed. Modelling allows for exploration of design spaces to fulfill system requirements, one of the advantages of modelling during the SDLC is that it provides indicative idea of the level of performance a design may provide. In this thesis performance relates to the time to solution for an application or the time for a benchmark to complete.

#### 2.2.1 Benchmarking

A benchmark is a simple application that is run that stresses a a system or subsystem, for example LINPACK [52] a linear algebra benchmark used to stress the computation power of a system and STREAM is designed to only stress the memory subsystem [92].

The TOP500 presents a list of the machines that perform well for LINPACK, more recently High Performance Conjugate Gradients (HPCG) has become increasingly common as a benchmark as this stresses a supercomputer similar to a production application [67]. HPCG uses a preconditioned CG method with a local symmetric Gauss-Seidel preconditioner.

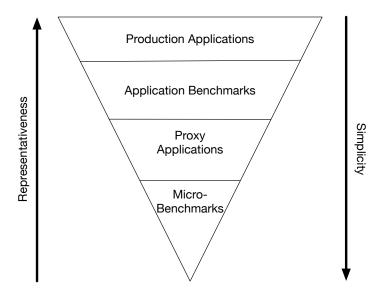

Benchmarks come in varying complexity from micro-benchmarks through to production applications like Sweep3D [80, 100, 53]. Given the complexity of modern parallel applications the rise of proxy/mini applications which capture some of the key resource characteristics (such as network traffic [78], computation [105]). Figure 2.2 shows the relationship of proxy applications to both production applications and microbenchmarks.

Figure 2.2: Representativeness and Simplicity of Applications Scale

#### **Network Benchmarks**

The usual approach to assessing the performance of massively parallel systems consists of executing a large set of benchmarks with a variety of differing communication patterns, often sequentially. How concurrently running applications interact with a machine's shared resources (i.e., the interconnect and parallel file system) is usually difficult to understand. As a result, these benchmarks fail to provide an accurate picture of application performance as they are unable to capture realistic network usage and highlight potential issues such as load imbalances that may affect the performance of collective operations [88].

ScalaBenchGen provides a way to automatically trace and replay applications as a synthetic MPI benchmark [130]. This approach uses the MPI Profiling layer (PMPI) to capture the MPI events which are stored chronologically; these events are then replayed through a custom tool. One limitation of ScalaBenchGen is that it provides no capability to scale communication sizes as multiple application traces must be captured with varying sizes.

File I/O can often interfere with MPI communications as large amounts of traffic are sent and received over the network. Dickson et al. have studied

the I/O characteristics of large applications by replicating I/O workloads with MACSio [50]. This is achieved by capturing Darshan [27, 28] logs of applications, parsing the log files and generating input parameters for MACSio. Darshan captures I/O characteristics from applications, this is achieved by wrapping the I/O function calls at link time. These additional functions handle the timing and statistics aggregation. Darshan does not store all I/O events like a an MPI trace tool such as Intel ITAC [70] but rather aggregates the data to characterise the I/O patterns reducing the data generated [27, 28].

Common MPI Benchmarks include the Intel MPI Benchmarks (IMB) [69], OSU Microbenchmarks (OSU) [104], and SKaMPI [110]. These microbenchmarks focus on the performance of singular MPI operations: either point-to-point or collective operations. They are useful when trying to diagnose application performance issues as they often report the average time for MPI operations. SKaMPI is no longer under active development but was extended to cater for complex communication patterns [64].

The NAS Parallel Benchmarks replicate commonly used application patterns to benchmark systems [12]. While this benchmark suite comprises a wide variety of parallel patterns it does not orchestrate them to show how the patterns can interact with or affect one another.

More recent benchmarks such as GPCNeT look at testing network performance in isolation and under load [36]. GPCNeT provides artificial noise in a network with four congestor patterns and is designed to stress a system rather than provide representative communication of a specific workload.

Task Bench is a parameterised benchmark for evaluating parallel systems [117]. It allows for rapid replication of a variety of programming models and applications. Configurable parameters allow the tuning of the length of the benchmark; the degree of parallelism; the type of kernel (such as a stencil or sweep) and tuning of any potential imbalance. This task-based approach is a novel idea that allows for flexibility and customisation. One drawback of this tool is that it only focuses on one task at a time meaning that it is difficult to understand how the

chosen benchmark will perform in a production environment.

I/O studies looking at improving performance are not new [5, 132, 14]. These studies typically focus on tuning I/O parameters for specific applications and systems. They often fail to consider the I/O subsystem being a shared resource and as such what contention may be affecting their performance.

Wright et al. have investigated the effects of I/O performance in relation to contention of the I/O nodes within a system [129]. They note that contention within the I/O subsystem can result in a 13% performance decrease on a multiuser system.

#### Limitations of Current Benchmarks

A large proportion of the benchmarks presented are designed to measure the peak network performance and often fail to test the advanced network features, the exception to this is GPCNeT which is designed inject noise in to the network to see the effects on common benchmarks. One issue with GPCNeT is that it splits the entire MPI Communicator randomly, this means that a congestor could reside on the same node and socket as a the benchmark under test. In reality production systems are configured to not mix applications on the same node or socket. Another limitation with GPCNeT is that it only provides microbenchmarks which are not representative to production applications and there is a missing understanding to how network congestion impacts application traffic.

In the literature there is no benchmark to stress the network and I/O concurrently, GPCNeT makes use of an incast traffic pattern to replicate I/O traffic which may not be representative as these patterns often neglect to factor a read/write time associated with performing the I/O.

#### 2.2.2 Performance Prediction

Performance predictions allow architects to understand performance characteristics of systems prior to the implementation. These typically come in two methods, analytical models and simulation.

#### Analytical

An analytic model is a mathematical representation of time required for some operation. This operation for HPC applications is typically the longest part of the execution or the cricitcal path of an application.

Common approaches to analytical network models include Bulk Synchronous Parallel (BSP) [126], LogP [39, 40] and LogGP [9].

The BSP model operates across *supersteps*, these steps consists of computation and a communication phase. At the start of a *superstep* synchronisation takes place then the computation can take place. If the data required is on a remote node then it must be retrieved during a previous *superstep*. In a communication phase then exchange data with other nodes.

The LogP model uses 4 parameters to model communication time:

- L Communication Delay (flight time of message latency)

- o Communication Overhead (time taken to transmit/recevie a message)

- g gap (minmimum time between consecutive messages)

- P number of processors

The LogP model assumes all messages are small, and in 1997 Alexandrov suggested the addition of a new parameter to cater for longer messages, called the LogGP model. The new parameter is the time *Gap per byte* and is the time taken to transmit a byte on the network.

In 1993 Adeve et al. showed that the performance of a parallel application could be modelled outside of strict modelling frameworks by taking a generic approach (see equation 2.4) [6].

$$T_{total} = (T_{computation} + T_{communication} + T_{overlap}) + T_{synchronisation} + T_{overhead}$$

$$(2.4)$$

In Equation 2.4 overlapping time from the communication and computation is taken in to account with  $T_{overlap}$ . Resource contention and system overhead

are considered independently in the model ( $T_{overhead}$ ) and any cost associated to synchronisation during the application run is catered with  $T_{synchronisation}$ . Each cost is calculated by either benchmarking, or timing sections of a code.

Once disadvantage of an analytical model is that there is an an underlying assumption that blocks of computation and synchronisation that place at the same time in lockstep and are deterministic which may not always be the case.

The use of reusable models has become prevalent with the development of a plug and play wavefront model [100]. This reduces the model development time, and increases the applicability of the model.

#### Simulation

Simulation is the recreation of some experimental setup with a computer based representation. This is usually performed with a simulator, these fall in to two categories Discrete-event driven and trace driven [72]. In Discreete-event simulations events are typically added to a queue and processed in chronological order. In contrast trace-driven simulations replay a trace of recorded events in which the order of execution is sequential.

There are limitations with a trace-driven simulation, these include:

- Scalability traces must be created on a physical system

- Flexibility traces can not be modified

There are many simulators covering different HPC system subsystems such as CPU, Memory and IO. Some notable examples of interconnect simulators include; SST/Macro [79], CODES [38], WARPP [66] and TraceR [71].

SST/Macro provides a macro simulation of the network using an analytical (MACRELS) and packet model (PISCES). MACRELS makes the assumption that data is moved as a single chunk while PISCES models individual packets moving through the network [79]. The packet model provides two levels of simulation: simple which assumes that packet flits travel as a single unit and are not separated; and cut-through which allows for the separation of flits but

provides an aggregated latency/bandwidth approximation for flits similar to MACRELS.

CODES [38] was designed to explore design questions around large-scale storage systems. It is built on top of the Rensselaer Optimistic Simulation System (ROSS) [29] which is a parallel discrete event simulation framework similar to SST. CODES has been developed to have a tightly coupled network model and this has been validated against an IBM BlueGene/L. A key feature of CODES is that, while it was designed for storage systems, it can be used to model collective performance for different topologies [98].

TraceR is a scalable simulator built on top of the parallel discrete event capabilities of CODES and ROSS allowing for scalable packet-level simulations of applications [71]. This is done by replaying communication traces through the simulation stack.

WARPP is macro simulation toolkit that predicts application runtime for applications by allowing you to recreate a communication pattern for the simulator and playing this through a system configuration. WARPP allows the modelling of core-to-core, socket-to-socket, and node-to-node configurations which are representative of modern HPC systems [66]. WARPP achieves these by using latency measurements of existing systems to approximate the timing for sending individual messages.

#### Limitations of Current Modelling Techniques

Analytical models fail to capture the advanced features that are present in modern low latency interconnection networks, for example if we consider two packets traversing a network that are freely available to be routed adaptively one packet could take the minimum path while the second could have additional hops in the network. In the case of a LogP or LogGP model then this would equate to differing values for o (the communication overhead).

Using simulation as a modelling technique allows for advanced network features to be modelling and accurately but this will only be the case if the simulator can reflect the crossbar and the input and output queues. SST/Macro provides some of this functionality but does not provide a cycle accurate router model which can cause implications when using this to design future networks. Given this it is impossible to model applications in a multi-user scenario.

One other area for concern with these modelling techniques is the validation process, while it is a good assumption to measure the latency between the links and compare against the simulation yet this fails to capture all the nuances of a system such as the memory latency and the host to NIC bus.

## 2.3 Low Latency Interconnect Design

This section explains the different aspects of a low latency interconnection network, it provides a description on the software communication stack that sits on top of the underlying hardware.

#### 2.3.1 Communication Stack

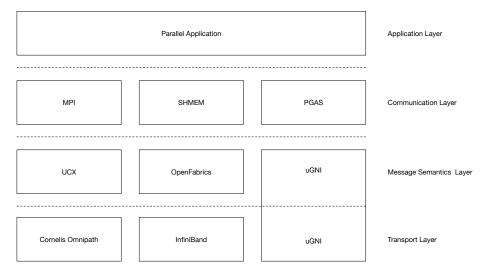

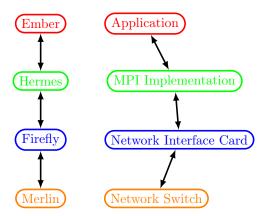

Figure 2.3 shows these different layers, similar to the Open Systems Interconnection (OSI) model.

Figure 2.3: Distributed Application Communication Stack

The application layer represents the parallel application. This is designed to

exploit the computational resources. This application is built with a communication library such as MPI or SHMEM. The communication library interfaces with the NIC drivers either through the kernel or through an additional library such as OpenFabrics Interfaces (OFI) libfabric [60], UCX [115] or Cray's uGNI [107]. Data is then transmitted over the network.

#### 2.3.2 Network Architecture

In this section we consider the hardware aspects of network design. This falls in to three key areas; firstly the network topology, secondly flow control and finally routing algorithms.

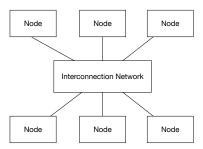

Figure 2.4 outlines an interconnection network. These networks differ from other Local Area Network (LAN) in the fact that they do not use a shared communication medium, instead each link is independent and can communicate without requiring to take control of the transmission medium. Examples of shared medium networks include Ethernet [3] and Wi-Fi [4].

Figure 2.4: Network Architecture

In the OSI model layer 2 frames are transported over the physical layer, multiple frames make up a packet at layer 3. In the case of low latency networks the smallest form of data movement is a flow control digit (flit). A physical digit (phit) is the smallest unit of data processed by a switch; multiple phits are combined to form a flit [44].

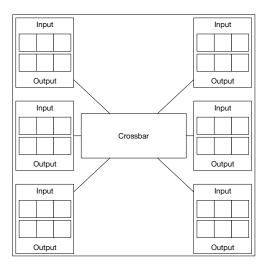

Figure 2.5 shows the basic architecture of a simplistic switch. Each of the ports has a input buffer and an output buffer, data then flows across the crossbar. This is common across most interconnects for example Cray Aries [54],

Intel Omni-Path [18] (now branded as Cornelis Omni-Path) and InfiniBand [1]. The switch radix refers to the number of ports available on a switch; for example a NVIDIA Mellanox InfiniBand Switch SB7800 consists of 36<sup>2</sup>; therefore has a switch radix of 36. The Cray Aries router has a switch radix of 64 [54].

Figure 2.5: Switch Architecture

#### Topologies

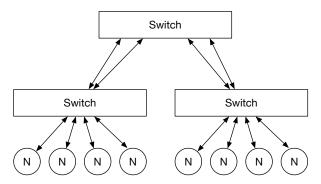

There are several key network topologies employed in low latency networks. The most common is the Fat-Tree [83].

Fat-Trees (also known as a folded Clos) are shaped similarly to a tree, and have root switches and leaf switches (see Figure 2.6). Typical implementations are 2 or 3 level and may be tapered between the root and leaf switches, reducing cost and increasing the number of available endpoints but at the expense of global bandwidth.

The worst case hop count is shown in Equation 2.5. If the left most node and the right most node want to communicate then it must go through each layer up and down in the tree but only hits the root switch once, this is only considered as 1 hop.

$<sup>^2 \</sup>mathrm{See}\ \mathsf{https://www.mellanox.com/related-docs/prod\_ib\_switch\_systems/pb\_sb7800.pdf}$

Figure 2.6: Fat-Tree Topology

Worst Case Hop Count =

$$(2 \times \text{Number of Levels}) - 1$$

(2.5)

Dragonfly is another network topology [76]; one key advantage of this topology is that this topology can be more cost effective for more endpoints than a Fat-Tree [76]. Networks based upon a Dragonfly are grouped in to three ranks, firstly the router, secondly a intra-group and thirdly inter-groups (see Figure 2.7). Figure 2.7 shows four nodes per router and three routers per group configuration with one global link per router for inter-group communication. The design of inter-group networks are left to the implementer, in the case of Cray Aries this is an All-To-All 2D mesh while NVIDIA's *Dragonfly+* implementation utilises a tapered Fat-Tree for the intra-group topology [116].

The Aries implementation from Cray of a Dragonfly utilises 4 nodes to 1 router and 96 routers per group connected as an All-To-All mesh electrically; the inter-group connections are optical and can be tapered reducing cost [54].

The average hop count for a Dragonfly is 5, this is where the node needs to communicate with a node from another group. The worst case could be higher than a fat tree for a sufficiently large network because the adaptive routing could make the data travel over multiple routers.

**Torus** are multidimensional topologies based upon a mesh or a cube network (k-ary n-mesh/cube network).

In 1977 Sullivan et al. document the first implementation of an n-cube net-

Figure 2.7: Dragonfly Topology - Group All-To-All

work [119, 120]. The requirement for this network design came from the performance constraint of one word being transmitted every instruction. Sullivan et al. show that the average propagation delay is  $\frac{n}{2}$ , with low link utilisation. Figure 2.8 shows a 2D torus, in a 3x3 grid, a switch (s in the figure) can then have multiple nodes attached.

More recent implementations of a torus topology include the Cray SeaStar [26, 8]. This features a 3D Torus, common configurations were 25x16x24 in size as seen in Titan [19].

Figure 2.8: Torus Topology, S is a Switch in which multiple nodes can reside

$\mathbf{HyperX}$  is an alternative to DragonFly topology for providing a high num-

ber of endpoints while reducing cabling and router count [7]. There are currently no commercially available implementations of a HyperX network. Figure 2.9 shows a 2D HyperX configuration, again multiple terminals can be attached to the switches (s in the diagram).

Figure 2.9: HyperX Topology, S is a Switch in which multiple nodes can reside

#### Flow Control Mechanisms

As low latency networks do not share a medium the transmission of data is controlled by other means. Flow control can be broken down in to two subcategories; buffered and bufferless. Bufferless flow control is the simplest flow control; packets are forwarded is resources are available or dropped/misrouted in the case where resources are not available. Buffered flow control stores the data until resources become available.

Buffered flow control can perform on both packets and flits. Store-and-forward and cut-through methods are examples of packet buffered flow control. Store-and-forward stores the packet until the all of the packet is received and then forwards it [44].

The latency of the packet is given in Equation 2.6.

$$T = Ht_r + H\left(\frac{L}{b}\right) \tag{2.6}$$

Cut-through does not wait for all of the packet to be received instead starts transmitting when resources become available [75]. This is sometimes known as virtual cut-through flow control and should not be confused with virtual channel flow control discussed later on. This approach reduces the latency for the packet compared to the store and forward method; Equation 2.7 shows the serialisation latency for cut-through.

$$T = Ht_r + \frac{L}{h} \tag{2.7}$$

Flit based buffered flow control methods include Wormhole Routing [43] and Virtual Channel Flow [42]. While Wormhole Routing contains routing in the title it is a flow control method. Wormhole routing works much like the packet based approach cut-through yet does not require the storage space of a packet just a flit. Issues arise when the output is blocked because there is insufficient resource available to forward the flit.

Virtual Channel Flow control provides multiple Virtual Channel (VC) per single physical channel overcoming the blocking problems of Wormhole as a flit can just utilise another virtual channel [42]. This approach improves channel bandwidth utilisation as it is not held idle while waiting to forward a blocked packet.

When buffering data at a switch, the switch must also know of the state if upstream buffers, this is controlled by one of three methods; credit-based flow control, on/off flow control and ack/nack flow control. In credit-based flow control the upstream router keeps count of the available flit buffers downstream. This count is decremented when a buffer is used; once this reaches 0 it must wait for the downstream switch to credit the upstream switch when it has forwarded a flit and a VC has become available [44]. For on/off flow control buffer state is handled with a control signal; when the flit has been received and the number

of buffers drops below a free buffers threshold the signal is turned off [44]. Once the number of free buffers rises above the threshold for re-enabling it is turned back on. The threshold for turning off the control signal should be greater than the relationship between time of additional flits being sent/received  $(t_{rt})$  after the signal changed state and the length  $(L_f)$  of the flit in bits (see Equation 2.8). This ensures that the buffers do not overflow.

$$F_{off} \ge \frac{t_{rt}b}{L_f} \tag{2.8}$$

In the case of ack/nack flow control a switch simply forwards a flit as it does not store upstream information. If the downstream switch has a buffer available then it replies with an Acknowledgement (ACK) [44]. If no buffer space is available then the flit is dropped and the downstream switch replies with a Negative Acknowledgement (NACK). This approach inefficient for both buffer space and bandwidth, due to flits being resent and have to be held on the upstream switch.

#### Routing Algorithms

Routing algorithms can either be oblivious or adaptive. Oblivious routing algorithms include Valiant's Routing algorithm [127] and minimal oblivious routing [101]. Oblivious routing algorithms route traffic irrespective of network load, compared to adaptive routing algorithms which will change the path data takes. In minimal oblivious routing traffic always takes the shortest path, in comparison Valiant's algorithm chooses a path at random to forward traffic.

Adaptive routing allows the traffic to be routed across different routes on a per flit basis based upon current state information, similar to changing the journey of a car due to traffic. Universal Globally Adaptive Load-balanced Routing (UGAL) is one approach to adaptive routing, traffic with this routing algorithm either take the minimal path or a non-minimal path [77, 108]. Congestion is avoided with this algorithm by using Valiant Load-balanced rout-

ing [125]. UGAL is commonly seen on Dragonfly topologies rather than a fat tree where minimal static routing provides the best performance.

## 2.4 Summary

This chapter has introduced types of parallelisation and the concept of speedup for parallel applications. Subtopics of performance engineering (benchmarking and performance modelling) have been introduced, the current state of the art for performance modelling and benchmarking has been discussed. The building blocks of a low latency interconnection network have been explained, which is further motivates the work presented in this thesis.

This thesis moves the state of the art forward for benchmarking by introducing a new flexible network and I/O benchmark called StressBench that allows for communication patterns to be concurrently across a system. Simulation is progressed with a reusable validation technique that been used to validate four systems and build performance models for two applications. Application performance predictions are then generated for a multi-user shared system demonstrating the usefulness this has on system procurement and network design.

# CHAPTER 3

## Compute Platforms and Applications

The hardware and software marry together to make the simulation of physics possible. In this chapter we discuss the hardware specifications of the computing resources used and the in depth view of the applications used throughout this thesis.

This chapter is as follows:

- Section 3.1 outlines the hardware configurations of the systems used throughout this thesis.

- Section 3.2 discusses the two primary applications used throughout this thesis in detail.

- Section 3.3 demonstrates common MPI implementations for communication patterns used by the applications mentioned in Section 3.2.

## 3.1 Compute Platforms

Modern HPC systems are typically interconnected servers which offer computation, storage and management. These servers are typically referred to as a node or blade. A node usually has 3 key elements, a CPU, RAM and NIC. The storage of a single node is typically irrelevant given that file systems are typically shared amongst all nodes. Common parallel filesystems include General Parallel File System (GPFS) [114] and Lustre [25].

Throughout this thesis the following compute platforms have been used extensively. These platforms differ in size, stage of lifecycle, CPU architecture as well as network architecture. The oldest system in use is Tinis, entering production in October 2015 and the newest system is Isambard entering production in November 2018.

The machines used in this thesis are significant because they cover a wide spectrum of what are considered supercomputers rather than a standalone compute server, from small clusters (Orac) to large machines such as Cori which was number 5 in the top500 when it entered production in 2016 [122]. One notable feature of these machines is that smaller machines typically use a Fat Tree network topology while larger machines may use a Dragonfly.

In the UK there are two tiers of HPC resources used by both academia and industry. Firstly we have the Tier 1 machine, currently called Archer2. This is one of the largest systems in the UK which features 5,860 nodes. Tier 2 machines are typically smaller in the 64-512 node sizes, for example Isambard. Universities may have their own smaller clusters such as Orac and Tinis. Given the large machine sizes there are typically resource limits dictated to stop resources being starved by large jobs. In the case for Tinis a user can request 32 nodes at one time without a reservation, where as on Archer2 the maximum job size is 1024 nodes. These constraints can be used to aid procurement decisions and scheduling requirements on a machine, for example on Cori the job scheduler will not allocate job sizes less than a group (384 nodes) to multiple groups as this significantly slows down the applications [37].

#### 3.1.1 Tinis

Tinis is a 212 node cluster featuring Intel Haswell (HSW) CPU and an InfiniBand interconnect. This machine is based at the University of Warwick. Table 3.1 shows the hardware specifications for Tinis. The systems is built using Lenovo NeXtScale nx360 M5 servers.

The software stack used on Tinis is GCC 8.3 and OpenMPI v4.0.3. The job scheduler for this system is Slurm.

Table 3.1: Tinis Specification

| Component           |                                             |

|---------------------|---------------------------------------------|

| CPU                 | 2 x Intel Xeon E5-2630 v3 2.4 GHz (Haswell) |

| Memory Per Node     | 64GB                                        |

| Network             | QLogic TrueScale InfiniBand (QDR)           |

| Network Topology    | 2-Level Tapered Fat Tree (2:1)              |

| Parallel Filesystem | GPFS                                        |

#### 3.1.2 Orac

Orac is a 84 node at the University of Warwick featuring Intel Broadwell (BDW) CPUs and an Intel Omni-Path low latency network. The specifications for Orac can be seen in Table 3.2. Orac is constructed from Lenovo NeXtScale nx360 M5 servers.

Table 3.2: Orac Specification

| Component           |                                               |

|---------------------|-----------------------------------------------|

| CPU                 | 2 x Intel Xeon E5-2680 v4 (Broadwell) 2.4 GHz |

| Memory Per Node     | 128GB                                         |

| Network             | Intel Omni-Path                               |

| Network Topology    | 2-Level Tapered Fat Tree (2:1)                |

| Parallel Filesystem | GPFS                                          |

The Intel compiler (v2020.4.304) was used for Orac with Intel MPI 2019 (2019.9.304).

#### 3.1.3 Isambard

Isambard is a tier 2 machine based on the Cray XC series; this machine makes use of the Marvell ThunderX2 CPU. This system uses XC50 blades. It features 329 nodes residing in 1 Dragonfly group.

OpenMPI 4.0.3 was used on Isambard, compiled with GCC using the Cray Programming Environment (9.0.6).

Table 3.3: Isambard Specification

| Component           |                                               |

|---------------------|-----------------------------------------------|

| CPU                 | $2 \times 32$ -core Marvell ThunderX2 2.1 GHz |

| Memory Per Node     | Phase 1: 256GB Phase 2: 512GB                 |

| Network             | Cray Aries                                    |

| Network Topology    | Dragonfly                                     |

| Parallel Filesystem | Lustre                                        |

#### 3.1.4 Cori

Cori (based at National Energy Research Scientific Computing Center (NERSC)) is a Cray XC40 System featuring both HSW and Knights Landing (KNL) CPU; the machine totaling 12,076 nodes (2388 HSW, and 9688 KNL nodes) makes use of 34 Dragonfly groups.

This split system design is similar to other large scale machines such as Trinity [51].

Table 3.4: Cori HSW Specification

| Component           |                                             |

|---------------------|---------------------------------------------|

| CPU                 | 2 x Intel Xeon Processor E5-2698 v3 2.3 GHz |

| Memory Per Node     | 128GB                                       |

| Network             | Cray Aries                                  |

| Network Topology    | Dragonfly                                   |

| Parallel Filesystem | Lustre                                      |