# Exploring the Capabilities of FPGA DSP Blocks in Neural Network Accelerators

by

Lenos Ioannou

Thesis

Submitted to the University of Warwick

in partial fulfilment of the requirements

for admission to the degree of

Doctor of Philosophy

### School of Engineering

November 2021

# Contents

| List of | Tables                                                                                           | $\mathbf{v}$ |

|---------|--------------------------------------------------------------------------------------------------|--------------|

| List of | Figures                                                                                          | vii          |

| Ackno   | vledgments                                                                                       | ix           |

| Declar  | tions                                                                                            | x            |

| 1       | Publications                                                                                     | . x          |

| 2       | Sponsorships and Grants                                                                          | . xi         |

| Abstra  | et                                                                                               | xii          |

| Acrony  | ms                                                                                               | xiii         |

| Chapte  | r 1 Introduction                                                                                 | 1            |

| 1.1     | Motivation $\ldots \ldots \ldots$ | . 2          |

| 1.2     | Aims and Objectives                                                                              | . 3          |

| 1.3     | Research Contributions                                                                           | . 4          |

| 1.4     | Thesis Organisation                                                                              | . 5          |

| 1.5     | Publications                                                                                     | . 7          |

| Chapte  | r 2 Background and Literature Review                                                             | 8            |

| 2.1     | Machine Learning Motivation                                                                      | . 8          |

| 2.2     | Real Time Signal and Image Processing                                                            |              |

|         | Systems                                                                                          | . 9          |

|         | 2.2.1 Convolution                                                                                | . 9          |

| 2.3     | Neural Networks                                                                                  | . 10         |

|         | 2.3.1 Fully Connected, or dense Layers                                                           | . 12         |

|         | 2.3.2 Convolutional layers-CNNs                                                                  | . 12         |

|         | 2.3.3 Recurrent Layers-RNNs                                                                      | . 14         |

|         | 2.3.4 Hyperparameters and Evaluation                                                             | . 16         |

| 2.4     | Compute Platforms                                                                                | . 17         |

|         | 2.4.1 Software Programmable Platforms $\ldots \ldots \ldots \ldots$                              | . 17         |

|         | 2.4.2 Application Specific Integrated Circuits (ASICs) $\ . \ .$                                 | . 19         |

|        | 2.4.3 Field-Programmable Gate Arrays (FPGAs)           | 20        |

|--------|--------------------------------------------------------|-----------|

| 2.5    | Compute Optimisations                                  | 23        |

|        | 2.5.1 Scheduling - Batch Inference                     | 23        |

|        | 2.5.2 Pruning                                          | 24        |

|        | 2.5.3 Reduced Precision-Quantisation                   | 25        |

| 2.6    | Enabling Faster Deployment on FPGAs                    | 25        |

|        | 2.6.1 High Level Synthesis (HLS)                       | 26        |

|        | 2.6.2 Overlays                                         | 26        |

|        | 2.6.3 Neural Network Toolflows                         | 27        |

|        | 2.6.4 Summary                                          | 29        |

| Chapte | er 3 Accelerating Neural Network Based Network Intru-  |           |

| sior   | n Detection on FPGA                                    | 30        |

| 3.1    | Introduction                                           | 30        |

| 3.2    | Background                                             | 31        |

| 3.3    | Related Work                                           | 32        |

| 3.4    | Experimental Methodology                               | 34        |

|        | 3.4.1 NSL-KDD Dataset                                  | 35        |

|        | 3.4.2 Software Implementation                          | 35        |

|        | 3.4.3 Hardware Implementation                          | 37        |

| 3.5    | Results and Evaluation                                 | 41        |

|        | 3.5.1 Network Throughput and Detection Rate            | 43        |

| 3.6    | Summary                                                | 44        |

| Chapte | er 4 High Throughput Spatial Convolution Filters using |           |

| FP     | GA DSP Blocks                                          | <b>45</b> |

| 4.1    | Introduction                                           | 45        |

| 4.2    | Related Work                                           | 46        |

| 4.3    | Generic Filter Architecture                            | 48        |

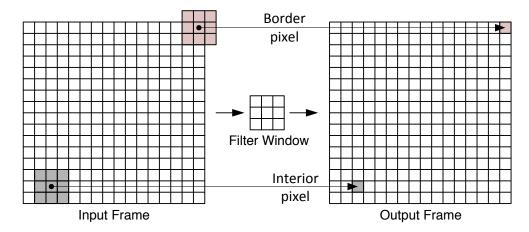

|        | 4.3.1 Boundary Handling                                | 49        |

| 4.4    | FPGA DSP Block Architecture                            | 50        |

| 4.5    | Filter Architecture                                    | 51        |

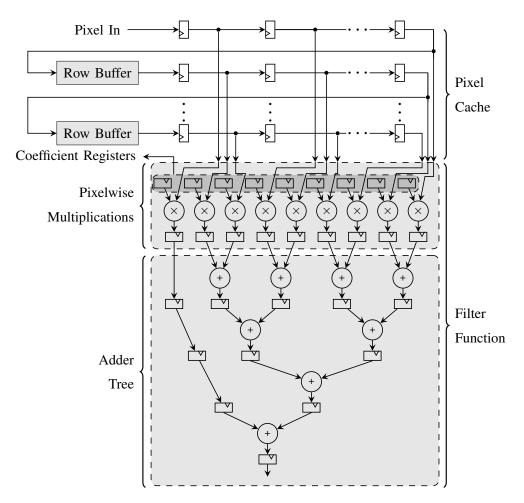

|        | 4.5.1 Filter Function $\ldots$                         | 52        |

|        | 4.5.2 Pixel Cache                                      | 52        |

|        | 4.5.3 Adder Tree                                       | 52        |

| 4.6    | Border Management Techniques                           | 55        |

| 4.7    | Proposed Architecture Results                          | 58        |

|        | 4.7.1 Adder Tree Designs in Direct Filter Structure    | 58        |

|        | 4.7.2 Direct Versus Transposed Form Architectures      | 59        |

|        | 4.7.3 Direct Filter Structure With Border Management   | 62        |

|        | 4.7.4 Comparison With Vivado HLS Filters               | 64        |

|       | 4.7.5          | Scalability Analysis                                  | 65       |

|-------|----------------|-------------------------------------------------------|----------|

|       | 4.7.6          | Comparisons With Previous Work                        | 66       |

| 4.8   | Summ           | nary                                                  | 68       |

| Chapt | er5I           | Lightweight Streaming Neural Network Overlay us       | _        |

| -     |                | A DSP Blocks                                          | 70       |

| 5.1   |                | luction                                               | 70       |

| 5.2   |                | ed Work                                               | 72       |

| 5.3   |                | and Fully Parallel Multiply Accumulate Operation Com- | 12       |

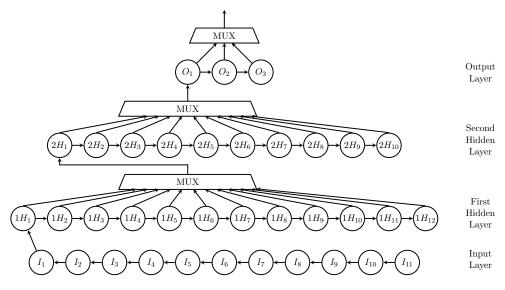

| 0.0   |                |                                                       | 73       |

| 5.4   | •              | mentation $\ldots$                                    | 75       |

| 0.4   | 5.4.1          | Overlay                                               | 75       |

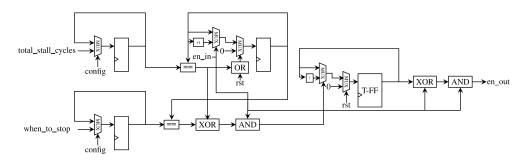

|       | 5.4.1<br>5.4.2 | Stall Mechanism                                       | 73<br>77 |

|       |                |                                                       |          |

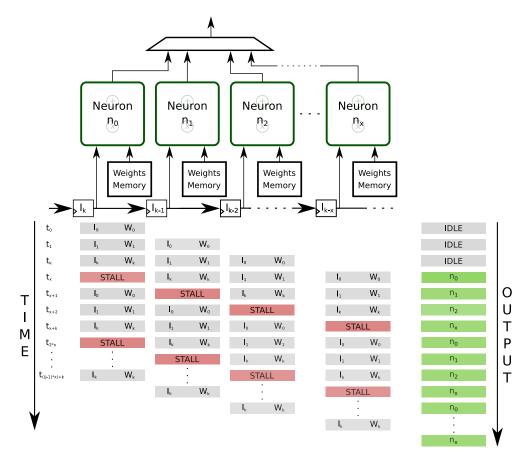

|       | 5.4.3          | Dataflow and Compute Timing Diagram                   | 78<br>79 |

|       | 5.4.4          | Case Study                                            | 78       |

| 5.5   |                | ts and Discussion                                     | 80       |

| 5.6   | Summ           | nary                                                  | 81       |

| Chapt | er 6 I         | Lightweight Streaming LSTM Neural Network Over        | -        |

| lay   | for FF         | PGA                                                   | 83       |

| 6.1   | Introd         | luction                                               | 83       |

| 6.2   | LSTM           | 1 Background                                          | 84       |

| 6.3   | Relate         | ed Work                                               | 85       |

| 6.4   | Propo          | sed LSTM Architecture                                 | 88       |

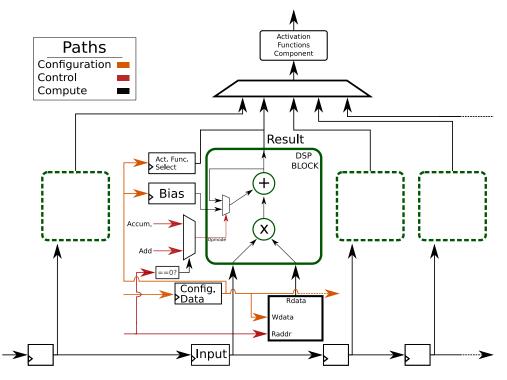

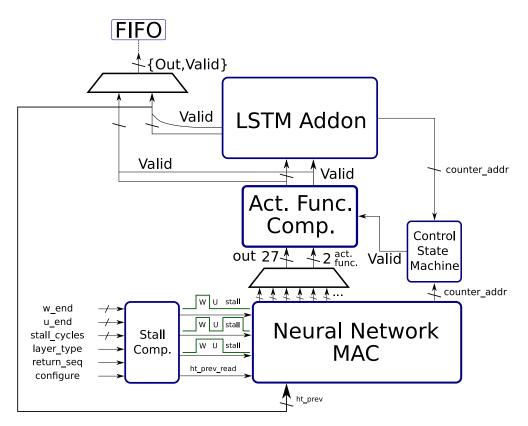

|       | 6.4.1          | Proposed Neuron Architecture                          | 88       |

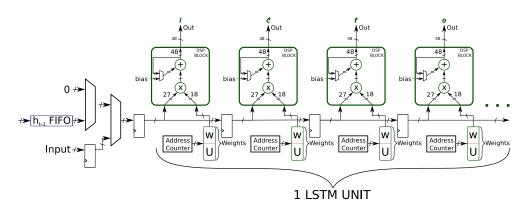

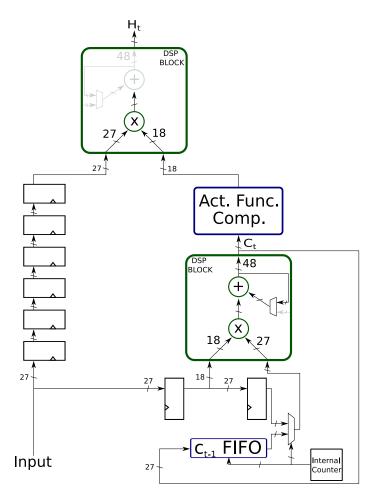

|       | 6.4.2          | Neural Network Multiply-Accumulate                    | 89       |

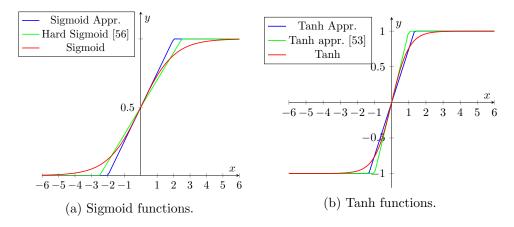

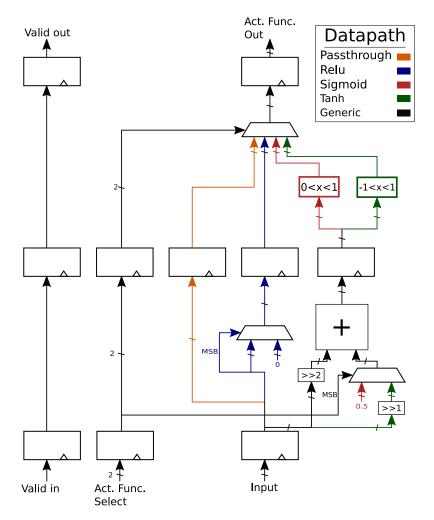

|       | 6.4.3          | Activation Function Approximation                     | 91       |

|       | 6.4.4          | LSTM Addon                                            | 95       |

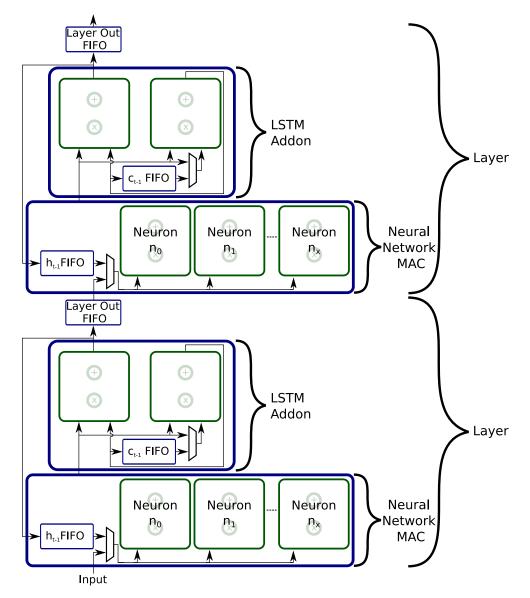

|       | 6.4.5          | Top Level Layer and Network Architecture              | 96       |

| 6.5   | Evalu          | ation                                                 | 99       |

|       | 6.5.1          | Models for Evaluation                                 | 99       |

|       | 6.5.2          | Activation Function Impact                            | 99       |

|       | 6.5.3          | Compute Overlap                                       | 100      |

|       | 6.5.4          | Weight Stationary Architecture                        | 101      |

|       | 6.5.5          | Performance, Resource Utilisation, and Comparisons    | 104      |

| 6.6   | Summ           | nary                                                  | 107      |

| Clark | on 7 (         | Complexing and Future Wards                           | 100      |

| -     |                | Conclusions and Future Work                           | 108      |

| 7.1   |                | hary of Contributions                                 | 109      |

|       | 7.1.1          | Intrusion Detection System at Line Rate Detection     | 109      |

|       | 7.1.2          | 2D Spatial Convolution Filters                        | 110      |

|     | 7.1.3  | Streaming Overlay Architecture for NN Computation                                                                         |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------|

|     |        | Based on FPGA DSP Blocks                                                                                                  |

|     | 7.1.4  | Streaming LSTM overlay architecture $\ . \ . \ . \ . \ . \ . \ . \ 111$                                                   |

| 7.2 | Future | Work                                                                                                                      |

|     | 7.2.1  | Overlay Generation Framework 111                                                                                          |

|     | 7.2.2  | Reduced Precision $\ldots \ldots 112$ |

|     | 7.2.3  | Efficient mapping and scheduling of irregular neural net-                                                                 |

|     |        | work workloads                                                                                                            |

|     | 7.2.4  | Support more layer types                                                                                                  |

|     | 7.2.5  | Support deep networks                                                                                                     |

| 7.3 | Summa  | ary                                                                                                                       |

# List of Tables

| 3.1 | Network configurations in related work                                                                                    | 34 |

|-----|---------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Accuracy results for training parameters                                                                                  | 36 |

| 3.3 | Test set classification results.                                                                                          | 36 |

| 3.4 | Accuracy comparisons on the NSL-KDD dataset                                                                               | 37 |

| 3.5 | Timing results for NN accelerator.                                                                                        | 41 |

| 3.6 | Resource utilisation on the Xilinx Zynq Z-7020                                                                            | 41 |

| 3.7 | Execution time                                                                                                            | 42 |

| 3.8 | Detection rate in packets.                                                                                                | 43 |

| 4.1 | Adder tree layout resource consumption                                                                                    | 53 |

| 4.2 | DSP Block usage for different configurations for a filter size of                                                         |    |

|     | $w \times w.\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots$ | 56 |

| 4.3 | Frequency and latency of direct form filter implementations with                                                          |    |

|     | different adder tree designs for $1280{\times}720$ frame, $7{\times}7$ filter and                                         |    |

|     | no border management.                                                                                                     | 59 |

| 4.4 | Resource utilisation of direct form filter implementations with                                                           |    |

|     | different adder tree designs for $1280{\times}720$ frame, $7{\times}7$ filter and                                         |    |

|     | no border management.                                                                                                     | 60 |

| 4.5 | Direct and transposed form implementation summary with                                                                    |    |

|     | $1280 \times 720$ frame and $7 \times 7$ filter.                                                                          | 61 |

| 4.6 | Direct LOG architecture for $1280\times720$ frame and $7\times7$ filter                                                   |    |

|     | with border policy from [107]                                                                                             | 63 |

| 4.7 | Relative resource utilisation and frequency for Vivado HLS filters.                                                       | 64 |

| 4.8 | Summarised previous work on 2-D spatial filters                                                                           | 67 |

| 5.1 | Latency and resource utilisation of the two compute methods                                                               | 74 |

| 5.2 | Case study neural networks configurations                                                                                 | 80 |

| 5.3 | Resource utilisation on the Zynq Ultrascale+ ZU7EV. $\ldots$ .                                                            | 80 |

| 5.4 | Theoretical timing results for the overlay                                                                                | 81 |

| 5.5 | Inferences per second on the different architectures                                                                      | 81 |

| 6.1 | Approximated functions equations                                                                                          | 92 |

| 6.2 | Approximated functions loss-Weather forecast                                                                              | 93 |

| 6.3  | Resource utilisation of the activation functions architecture $95$ |

|------|--------------------------------------------------------------------|

| 6.4  | Approximated functions loss/accuracy-MNIST 99                      |

| 6.5  | Approximated functions loss-Character level LSTM 100               |

| 6.6  | Compute overlap when processing LSTMs                              |

| 6.7  | Weights to input size ratio                                        |

| 6.8  | Resource utilisation and performance comparisons with same         |

|      | models                                                             |

| 6.9  | Resource utilisation and performance comparisons with different    |

|      | models                                                             |

| 6.10 | Resource utilization and frequency on Zynq 7000 series 106         |

# List of Figures

| 2.1  | Convolution operation showing the source image, overlapping         |          |

|------|---------------------------------------------------------------------|----------|

|      | kernel window and result image [26]                                 | 10       |

| 2.2  | Neuron Structure, showing the inputs, weights, biases and ac-       |          |

|      | tivation function [12].                                             | 11       |

| 2.3  | Artificial neural network structure                                 | 12       |

| 2.4  | A typical CNN structure, showing the distinct feature extraction    |          |

|      | and classification parts [44].                                      | 13       |

| 2.5  | Per layer number of operations in AlexNet [13]                      | 13       |

| 2.6  | Per layer number of weights in AlexNet [13]                         | 14       |

| 2.7  | A recurrent unit, its unrolled computation over timesteps [48].     | 14       |

| 2.8  | An LSTM unit.                                                       | 15       |

| 2.9  | Systolic Array dataflow used in Google Edge TPU [64].               | 20       |

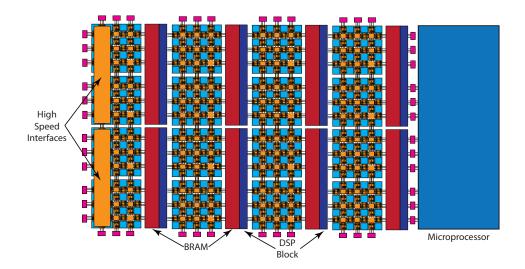

| 2.10 | A part of an FPGA architecture, showing the various building        | -        |

|      | blocks. [65]                                                        | 21       |

| 2.11 | DSP48E1 compute block architecture, showing the various             |          |

|      | datapaths, compute units and configurations [71]                    | 22       |

| 2.12 | FPGA SoC architecture showing the reconfigurable fabric along       |          |

|      | with a microprocessor [65].                                         | 23       |

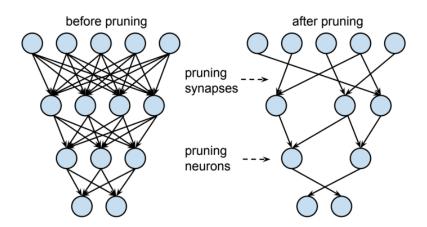

| 2.13 | Pruned Neural Network example, showing weight (synapse) and         |          |

|      | neuron pruning [74]. $\ldots$                                       | 24       |

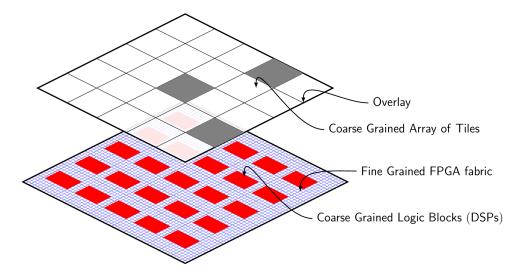

| 2.14 | Coarser grained overlay architecture on top of the finer grained    |          |

|      | reconfigurable fabric [79]                                          | 27       |

|      | Grant (1-)                                                          | -        |

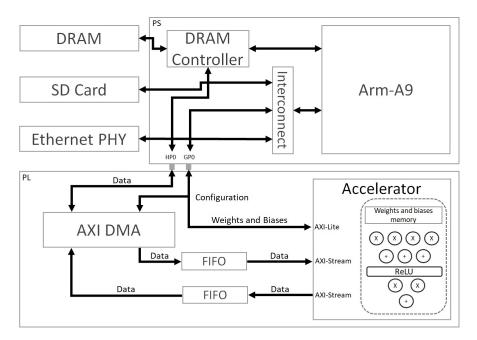

| 3.1  | Overview of the Xilinx Zynq based system architecture               | 38       |

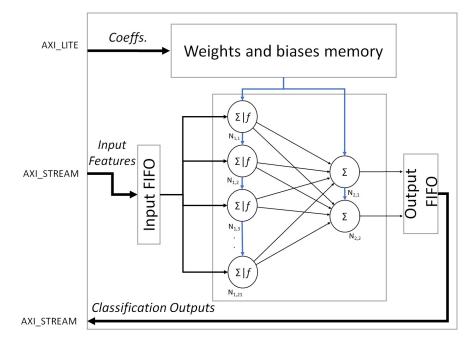

| 3.2  | Intrusion Detection System diagram, showing the various memor-      |          |

|      | ies, neurons and connectivity                                       | 39       |

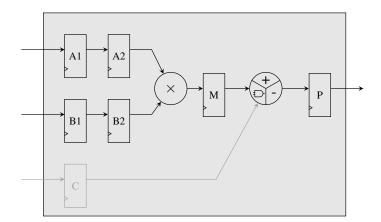

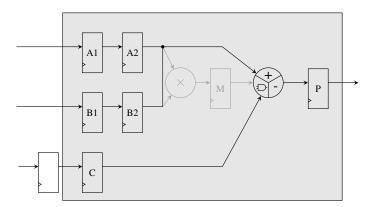

| 4.1  | Filter architecture diagram, showing the various functional blocks. | 48       |

| 4.2  | 2-D filter operation showing indicative examples for interior and   | 10       |

| 1.2  | border pixels                                                       | 50       |

| 4.3  | Transposed filter diagram, showing the various compute blocks       |          |

| 1.0  | and pipeline stages [98]                                            | 51       |

|      |                                                                     | <u> </u> |

| 4.4  | DSP48E1 block diagram for multiplication.                         | 53 |

|------|-------------------------------------------------------------------|----|

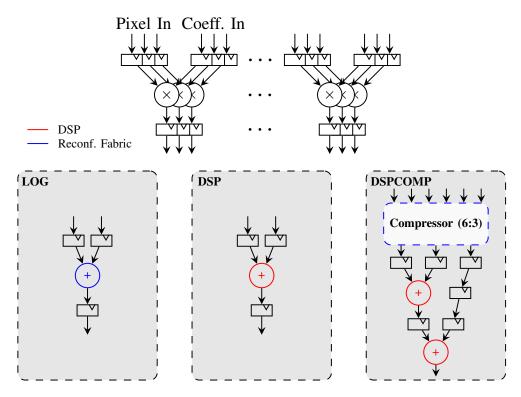

| 4.5  | Alternative adder tree layouts: LOG, DSP, and DSPCOMP             | 54 |

| 4.6  | DSP48E1 block diagram for addition.                               | 55 |

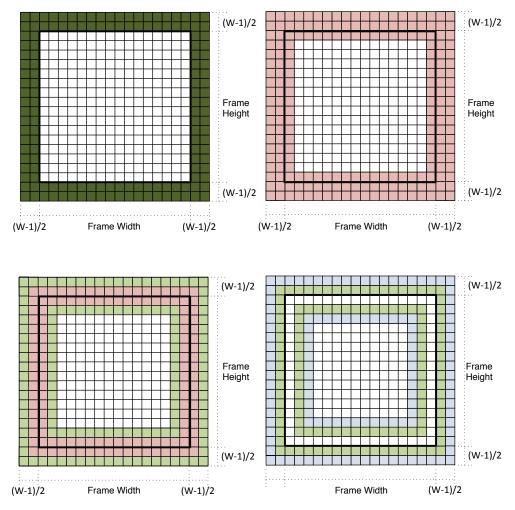

| 4.7  | Border management techniques (top left: constant extension, top   |    |

|      | right: border extension, bottom left: mirroring with duplication, |    |

|      | bottom right: mirroring without duplication) [99]                 | 57 |

| 4.8  | Implementation results of the proposed filter architecture on     |    |

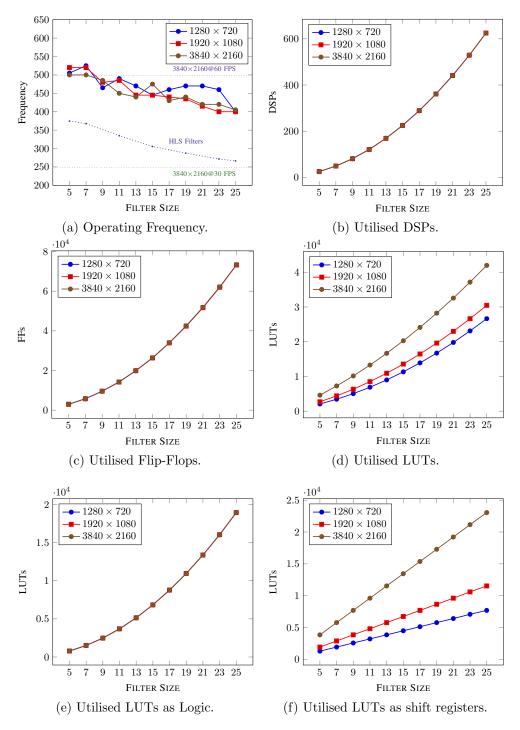

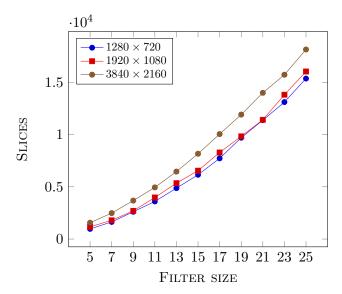

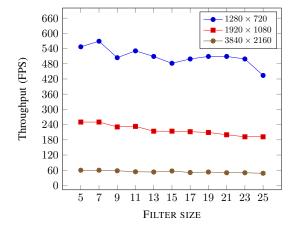

|      | three image resolutions, each on 11 filter sizes                  | 62 |

| 4.9  | Slice utilisation for each filter implementation.                 | 65 |

| 4.10 | Achievable frame rates for varying filter and frame sizes         | 66 |

| 5.1  | Fully Unrolled Multiply-Accumulate tree Architecture              | 73 |

| 5.2  | Serial Compute Architecture, using DSP blocks                     | 74 |

| 5.3  | Diagram that shows configuration, control and compute paths       |    |

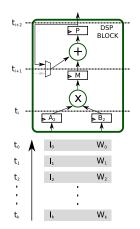

|      | for each neuron compute unit                                      | 75 |

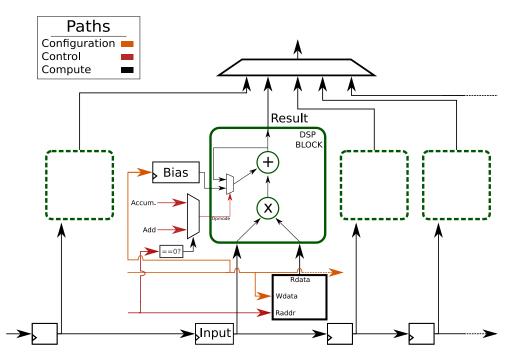

| 5.4  | Proposed neural network overlay architecture, mimicking the       |    |

|      | structure of the network                                          | 76 |

| 5.5  | Programmable stall mechanism enabling variable sized networks     |    |

|      | to be implemented                                                 | 78 |

| 5.6  | Diagram that shows the dataflow and compute allocations over      |    |

|      | time-steps                                                        | 79 |

| 6.1  | Neuron Architecture showing the configuration, control and        |    |

|      | compute paths                                                     | 89 |

| 6.2  | Neural Network Multiply-AccumulateArchitecture                    | 90 |

| 6.3  | Activation functions and their approximations                     | 93 |

| 6.4  | Activation functions architecture, showing the various datapaths, |    |

|      | logic blocks and pipeline stages                                  | 94 |

| 6.5  | LSTM addon compute architecture, showing the various logic        |    |

|      | elements and delay registers.                                     | 95 |

| 6.6  | Top level layer architecture                                      | 96 |

| 6.7  | Top level Neural Network architecture                             | 98 |

|      |                                                                   |    |

# Acknowledgments

First and foremost I would like to thank my supervisor, Dr. Suhaib Fahmy, for giving the opportunity to study for my PhD under his guidance. His feedback has been invaluable during my studies at Warwick, while our meetings and discussions helped me grow as a researcher and a person. He always took the time to help me improve my technical writing and to answer even my most tedious questions. His enthusiasm and support even in the most hectic periods will guide me forever.

I would also like to thank all the people I have met at the University of Warwick, especially the PhD students (Ryan, Alex and Kusuma), post-docs and other students at the WARC lab. Their company and discussions have made the daily routine better in so many ways.

I am also very thankful to my friends back home, who have always made the getaways from my studies more fun and relaxing.

Finally, I am eternally grateful to my family, especially my parents, Ntinos and Stella, for their unconditional support and understanding, in particular throughout my studies. I am also very thankful to my grandmother Rita, with whom I spent a lot of time growing up and helped shape the person I am today.

# Declarations

### 1 Publications

Parts of this thesis have been previously published by the author in the following:

- L. Ioannou and S. A. Fahmy. Network Intrusion Detection Using Neural Networks on FPGA SoCs. In Proceedings of the International Conference on Field Programmable Logic and Applications (FPL), pages 232–238, 2019.

- [2] L. Ioannou and S. A. Fahmy. Neural Network Overlay Using FPGA DSP Blocks. In Proceedings of the International Conference on Field Programmable Logic and Applications (FPL), pages 252–253, 2019.

- [3] L. Ioannou and S. A. Fahmy. Lightweight Programmable DSP Block Overlay for Streaming Neural Network Acceleration. In Proceedings of the International Conference on Field-Programmable Technology (ICFPT), pages 355–358, 2019.

- [4] L. Ioannou, A. Al-Dujaili, and S. A. Fahmy. High Throughput Spatial Convolution Filters on FPGAs. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, 28(6):1392–1402, 2020.

- [5] L. Ioannou and S. A. Fahmy. Streaming Overlay Architecture for Lightweight LSTM Computation on FPGA SoCs. Submitted to: ACM Trans. Reconfigurable Technol. Syst..

### 2 Sponsorships and Grants

This research was funded by the UK Engineering and Physical Sciences Research Council (EPSRC), grant EP/N509796/1, and the School of Engineering, University of Warwick, UK.

## Abstract

Neural networks have contributed significantly in applications that had been difficult to implement with the traditional programming concepts (e.g. computer vision, natural language processing). In many occasions, they outperform their hand coded counterparts and are increasingly popular in end user applications. Neural networks, however, are compute and memory demanding, making their execution in resource constraint devices more difficult, especially for real time applications. Custom computing architectures on Field-Programmable Gate Arrays (FPGAs) have traditionally been used to accelerate such computations to meet specific requirements. Nonetheless, most approaches in the literature do not consider in detail the underlying FPGA architecture, resulting in less efficient implementations. They additionally have focused on complex designs optimised for high throughput in a datacenter setting with access to large datasets in memory. Meanwhile real edge applications are often processing streaming sensor data and require consideration of efficiency. Detailed FPGA implementations involve time consuming low level design effort, which in turn result in long turnaround time. FPGAs have evolved over the years to include hard macro blocks, for example Digital Signal Processing (DSP) blocks, that map more efficiently widely used operations. In addition, FPGAs are often tightly coupled with embedded microprocessors in a System-on-Chip (SoC) arrangement that offers a complete system solution. This thesis explores the capabilities of FPGA DSP blocks in neural network accelerators. Within this context, practices and tools that improve turnaround time have been explored, drawing conclusions on how to exploit DSP blocks in a way that maximises performance and efficiency. Finally, the work in this thesis shows that designing overlays in an architecture-centric manner can result in high operating frequency, while scaling to better utilise FPGA resources.

## Acronyms

- ALU Arithmetic Logic Unit.

- **API** Application Programming Interface.

- **ASIC** Application Specific Integrated Circuits.

- **AXI** Advanced eXtensible Interface.

- **BRAM** Block Random Access Memory.

- **CLB** Configurable Logic Block.

- **CNN** Convolutional Neural Networks.

- CPU Central Processing Unit.

- **CSD** Canonic Signed Digit.

- CUDA Compute Unified Device Architecture.

- **DA** Distributed Arithmetic.

- **DBN** Deep Belief Network.

- **DDoS** Distributed Denial of Service.

- **DMA** Direct Memory Access.

- **DNN** Deep Neural Networks.

- **DNNDK** Deep Neural Network Development Kit.

- **DoS** Denial of Service.

- **DPU** Deep-learning Processor Unit.

- **DRAM** Dynamic Random Access Memory.

- **DSP** Digital Signal Processing.

- ${\bf DT}\,$  Decision Trees.

${\bf FF}\,$  Flip-Flop.

- **FIFO** First In First Out.

- **FIR** Finite Impulse Response.

- FPGA Field-Programmable Gate Array.

- **FPS** Frames Per Second.

- **Gbps** Giga bits per second.

- GFLOPs Giga Floating-Point Operations per second.

- **GOPs** Giga Operations Per second.

- GPU Graphics Processing Unit.

- **GRU** Gated Recurrent Unit.

- HD High Definition.

- HDL Hardware Description Languages.

- HLS High Level Synthesis.

- **IDS** Intrusion Detection System.

- **IoT** Internet of Things.

- **IPC** Instructions Per Cycle.

- **IPv4** Internet Protocol version 4.

- LSTM Long-Short-Term Memory.

- **LUT** Look-Up-Table.

- MAC Multiply-Accumulate.

- **MAE** Mean Absolute Error.

- MIO Multiplexed Input Output.

- ML Machine Learning.

- NDAE Non-symmetric Deep Auto-Encoder.

- **NN** Neural Networks.

- PCA Principal Component Analysis.

- $\mathbf{PL}$  Programmable Logic.

- **PR** Partial Reconfiguration.

- ${\bf R2L}\,$  Remote to Local.

- **RAM** Random Access Memory.

- **ReLU** Rectified Linear Unit.

- ${\bf RF}\,$  Random Forests.

- **RISC** Reduced Instruction Set Computing.

- **RNN** Recurrent Neural Networks.

- **ROM** Read Only Memory.

- ${\bf RTL}\,$  Register-Transfer Level.

- **SAD** Sum of Absolute Differences.

- ${\bf SIMD}\,$  Single Instruction Multiple Data.

- ${\bf SoC}\,$  System-on-Chip.

- **SOM** Self Organising Maps.

- **SRL** Shift Register Look-up-table.

- **SVM** Support Vector Machine.

- **TPU** Tensor Processing Unit.

- **U2R** User to Root.

- **VHDL** VHSIC Hardware Description Language.

- **VHSIC** Very High Speed Integrated Circuit.

- **VLIW** Very Long Instruction Word.

## Chapter 1

## Introduction

The emergence of Machine Learning (ML) has enabled a plethora of applications that would be more difficult to implement with the traditional programming methods. Although ML concepts have been reported in the literature for many years, the availability of large volumes of data, through big data, coupled with faster training turnaround time due to the availability of highly parallel compute platforms and other algorithmic and mathematical optimisations, have recently enabled ML models to outperform manually programmed solutions in more problem domains. Hence, ML has attracted the research interest of many disciplines, among them computer engineering, in which this thesis lies.

Machine Learning approaches span a wide range of learning techniques, supervised or unsupervised, and a variety of models, Self Organizing Maps (SOM), Support Vector Machines (SVM), Neural Networks (NNs), Decision Trees (DT), and many more [6]. The versatility and more complex structure of NNs has rendered them more capable to model non-linear tasks more accurately, compared to the other options. Therefore, NNs have been widely used in a wide spectrum of applications, from healthcare [7] to computer vision [8].

The operation of ML models comprises two phases, *training* and *inference*. During training, the ML model is formed and refined using a dataset to determine the best parameters to achieve a required task, iteratively refining to reduce the prediction error. During inference, the trained model is used to make predictions, based on the learned parameters, on new, unseen data. Training comprises the heaviest workload of the two and usually takes place offline on highly parallel computing platforms. Indicatively, it can take from a few hours to a few days, depending on model's topology. Inference can potentially take place on any compute device, from highly powerful servers to extremely constrained edge devices. Nonetheless, minor adjustments, i.e. fine-tuning, of the trained model's parameters may be made to better suit the specific use patterns of the device or user, either on device or centrally.

Due to the more central nature of training, inference has been the main

target of various optimisations in an effort to meet the needs and capabilities of different devices across the computing spectrum. Edge devices have been a key focus since they impose stricter and more challenging attributes, e.g. latency, throughput, energy, etc. Moreover, due to the variable and often prohibitive transfer latency to the cloud, real time edge devices must perform their computations locally [9]. One approach to meet strict constraints has been with the use of custom computing architectures, either Application Specific Integrated Circuits (ASICs) [10, 11] or implemented on FPGAs [12–14]. Custom computing architectures can be tailored to meet a device's specifications, at the cost of flexibility compared to more general computing platforms, e.g. CPUs and GPUs. FPGAs have continued to improve in terms of performance and efficiency, primarily due to architectural evolutions that incorporate a variety of hard macro blocks. Moreover, complete System-on-Chip (SoC) solutions, featuring a low power processor tightly coupled with an FPGA fabric, are ideal for edge solutions in which a generic processor is supported by an accelerator on an FPGA.

Although, FPGAs are not superior to ASICs in terms of raw characteristics, their off-the-shelf availability, which in turn results in smaller turnaround time, reduced cost as well as their reconfigurable operation render them an excellent solution for acceleration, especially in domains where the computational algorithms continue to evolve, such as ML. We therefore have the opportunity to explore new approaches that better take advantage of the capabilities of modern FPGAs to maximise their effectiveness.

### 1.1 Motivation

The increasing ubiquity of interconnected devices at the edge has provided the means to automate various daily tasks through the use of sensors and actuators integrated with these devices. We therefore, have the ability to collect unprecedented volumes of data and the means to automate actions through the use of NNs. However, as the increasing interconnectivity of smart devices provides a plethora of even more advanced capabilities, it simultaneously renders efficiency more important. Edge devices are often battery powered, to enable portability, and of reduced processing power, supporting a subset of the instruction set of desktop computers. Custom computing architectures on FPGAs can therefore be used to provide real time performance and high energy efficiency at the edge.

NNs are extremely demanding in terms of memory requirements, to store the trained model's coefficients and intermediate results of computation, in addition to the significant computational workload they entail. Even a relevantly small NN may have such memory requirements that on-chip storage does not suffice,

requiring frequent off-chip memory transfers that are costly in terms of energy and latency. The significant computational workload mainly consists of matrixvector and matrix-matrix multiplications. In addition, edge devices are often dealing with data that streams from the various sensors or other components, e.g. camera, microphone etc.. Therefore ML computations should ideally be optimised around this streaming dataflow, which can add complexity to the design of custom architectures.

The design of custom computing architectures on FPGAs using Hardware Description Languages (HDLs), e.g. Verilog or VHDL, at Register-Transfer Level (RTL) involves time consuming low level design effort. However, machine learning workloads differ in their parameters and structure, therefore accelerator architectures should be scalable and easily reconfigured to different model parameters and configurations. To this end, High Level Synthesis (HLS) has emerged as an alternative to traditional RTL design, essentially raising the programming domain to a higher level language, e.g. C, with guided automated translation into an architecture. Another option is to build an abstracted overlay architecture that is fundamentally flexible enough to adapt to varying NN model topologies.

Most compute architectures on FPGAs are designed as static solutions, not fully taking advantage of the reconfigurable nature of the FPGAs. In addition, there is often very little consideration of the underlying FPGA architecture, resulting in implementations that operate at well below the frequencies that are theoretically achievable, hence not fully exploiting the capabilities of the device. Maximising device capabilities is key to meeting strict specifications in a challenging domain.

### 1.2 Aims and Objectives

This work in this thesis aims to explore the more efficient use of the underlying FPGA architecture and macro blocks for lightweight NNs on devices at the edge, while maintaining flexibility within this domain. This in turn is expected to result in a computing architecture that achieves higher operating frequency and hence performance, while offering higher energy efficiency through better resource utilisation. Lastly, since this thesis targets edge devices, all implementations are aimed to be integrated in an SoC environment, considering a streaming dataflow model.

Therefore, the aforementioned aims result in the following objectives:

• Use of Digital Signal Processing (DSP) blocks: NNs involve a significant amount of Multiply-Accumulate (MAC) operations that can be more efficiently mapped to the DSP macro blocks on modern FPGAs. This is expected to yield implementations that offer:

**High operating frequency:** which is expected to contribute to achieving higher performance in terms of latency and throughput.

**Higher energy efficiency:** since functions implemented on the FPGA's macro blocks consume less power than their equivalent implementations in fabric [15]. Moreover, higher operating frequency can contribute partly to energy efficiency, since leakage currents are clock independent [16].

- **Programmability-Abstractions:** Although FPGAs are reconfigurable, the lengthy design and compilation times result in less flexible deployments. Enabling more rapid deployment, through the use of higher level languages or coarse grained overlays, would improve the flexibility of FPGA design.

- Streaming dataflow: FPGA SoCs, and edge devices in general, often collect and distribute data in a streaming fashion, not using highly parallel bulk transfers that are used with more datacenter oriented interconnect such as PCI Express. Such dataflow architectures are more difficult to efficiently scale in terms of performance since data availability is less abundant. Therefore, an architecture that tailors the operation of its compute units and dataflow to a streaming arrangement would be better suited for the edge domain.

- **Parallelism:** NNs consist of highly parallel workload from which improved performance can be obtained by unrolling these computations. The unrolling scheme, however, must be tailored to the streaming data-flow.

### **1.3** Research Contributions

The research contributions of this thesis comprise computing architectures, implemented on FPGAs, that accelerate NNs, or part of their computations. The implemented architectures have been evaluated mainly in terms of performance and resource utilisation. Occasionally, additional features have been derived in order to normalise the varying capabilities between different FPGA devices and make more objective comparisons with previous work.

More specifically, the research contributions of the work in this thesis are as follows:

• An exploration an Intrusion Detection System (IDS) application using NNs on an FPGA SoC, implemented with HLS. The IDS demonstrated improved detection times while offering coefficient re-programmability along with the use of floating point operations, setting a baseline for the complexity of a parallel but not highly optimised architecture.

- An exploration of various large scale 2-D spatial convolution filters on modern image resolutions that is heavily optimised around modern FPGA DSP blocks. A detailed investigation of scalability for different filter sizes and image resolutions, along with their impact on operating frequency and resource utilisation, is performed. Comparisons made with previous work and equivalent implementations with HLS motivate the work that follows thereafter in this thesis.

- An FPGA overlay architecture, tailored to the compute patterns of specific NN layers and built around the concept of DSP block as a neuron. The overlay processes a streaming flow of data, is implemented in an FPGA SoC environment, and is runtime programmable. The overlay achieves high operating frequency and demonstrates improved performance compared to mobile, desktop CPU, and relevant previous work on FPGAs.

- An enhanced version of the aforementioned overlay architecture to support a wider variety of layer types including Long Short-Term Memory (LSTM) that require complex feedback structures. This overlay is shown to scale with a small frequency overhead, while extensive comparisons with previous work demonstrate the benefits of the proposed approach.

### 1.4 Thesis Organisation

Chapter 2 presents relevant background information on Machine Learning and Neural Networks in particular, followed by the different compute platforms and the various algorithmic optimisations, in addition to a literature review. This includes details on basic NN building blocks, including different layer types and activation functions. More information follows on various compute platforms, focusing mainly on modern FPGAs and the different methods and tools to enable more rapid deployment.

Chapter 3 demonstrates an NN application for network intrusion detection on an FPGA SoC device. Initially, the NN is trained in software, followed by architecture generation using HLS. The architecture is flexible, to allow coefficient modification at runtime, while using 32-bit floating point arithmetic throughout. The HLS generated design is integrated in an SoC implementation, alongside an ARM-A9 embedded processor, and has been functionally tested. The chapter concludes with comparisons with equivalent software implementations and previous work, showing improved detection time. Chapter 4 explores FPGA implementations of spatial convolution filters, using Verilog HDL, focusing on modern image resolutions and respectively scaled filter sizes. The different design choices for the selected architecture are substantiated by comparisons on indicative designs, followed by an exploration on how the selected architecture scales and, finally, comparisons with HLS equivalent implementations. The work in this chapter motivates the transition from HLS to a more architecture-centric design approach that is better suited to the capabilities of the FPGA architecture, specifically DSP blocks and their runtime flexibility. Moreover, the extensive range of filter sizes demonstrates that the proposed architecture scales well in terms of frequency, laying the groundwork for the chapters that follow.

Chapter 5 presents an overlay implementation of feed forward NNs, using streaming dataflow with the FPGA DSP blocks acting as individual neurons. The implemented architecture achieves high operating frequency and better performance compared to software equivalents and previous work on HLS. The overlay has been integrated in an SoC implementation, operating at a baseline frequency, and has been functionally tested. Although the baseline NNs used in this chapter do not stress the scalability and the functionality of the overlay significantly, they serve as a stepping stone for the more complex overlay that follows.

Chapter 6 presents an expanded overlay streaming architecture that supports an additional set of NN layers, most notably LSTMs that require feedback, as well as more flexible activation functions. The overlay in this chapter is shown to scale at a low frequency overhead, while the extensive comparisons between the implemented overlays in this chapter and previous work demonstrate and quantify the effectiveness of the proposed approach.

Chapter 7 concludes the work presented in this thesis and discusses future work based on its findings.

### 1.5 Publications

The originality of the research contributions of this thesis is demonstrated through publications in the following peer-reviewed conference and journal proceedings:

- L. Ioannou and S. A. Fahmy. Network Intrusion Detection Using Neural Networks on FPGA SoCs. In *Proceedings of the International Conference* on Field Programmable Logic and Applications (FPL), pages 232–238, 2019 [1].

- L. Ioannou and S. A. Fahmy. Neural Network Overlay Using FPGA DSP Blocks. In Proceedings of the International Conference on Field Programmable Logic and Applications (FPL), pages 252–253, 2019 [2].

- L. Ioannou and S. A. Fahmy. Lightweight Programmable DSP Block Overlay for Streaming Neural Network Acceleration. In Proceedings of the International Conference on Field-Programmable Technology (ICFPT), pages 355–358, 2019 [3].

- L. Ioannou, A. Al-Dujaili, and S. A. Fahmy. High Throughput Spatial Convolution Filters on FPGAs. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, 28(6):1392–1402, 2020 [4].

- L. Ioannou and S. A. Fahmy. Streaming Overlay Architecture for Lightweight LSTM Computation on FPGA SoCs. Submitted to: ACM Trans. Reconfigurable Technol. Syst. [5].

### Chapter 2

# Background and Literature Review

Edge devices' functionalities have evolved over the years, from passive to more interactive, incorporating sensors and actuators to interact with the physical world in a smarter way. Meanwhile, the increasing interconnectivity of such devices has enabled the collection of unprecedented volumes of data, from which specific patterns can be extracted and used for better informed future predictions and user tailored operation. Machine Learning has provided the means to automate this learning process and in many cases has outperformed hand coded methods of extracting such patterns. Neural Networks are considered by many the most prominent class of ML models, and are nowadays increasingly used on wide spectrum of computing devices, from highly parallel platforms to resource constrained edge devices. As a result, there is great interest on the workload and size of Neural Networks and how these can be executed more efficiently on various platforms through various optimisations, either algorithmic or architectural. This chapter covers all aforementioned aspects in theoretical background and relevant literature review.

### 2.1 Machine Learning Motivation

ML algorithms were shown to generalise their learned patterns to new, previously unseen data. The latter, renders them very useful to simple day to day tasks, but more importantly, to more complex tasks that have greater impact, for example network security applications. Specifically, ML algorithms have the potential to detect new, zero-day, attacks or even modified known attacks that have been altered adequately to deceive security mechanisms. Both of which are very difficult to detect with hand coded rules. Therefore, there is plenty previous work in the literature that explored the use ML in security applications, in the context of an Intrusion Detection System (IDS). The work in [17] explored the use of Non-symmetric Deep Auto-Encoders (NDAE) and Random Forests (RF) for network intrusion detection, demonstrating great potential in their detection results and improved turnaround time compared to a Deep Belief Network (DBN). The use of Neural Networks in the same domain was explored in [18–23], obtaining high detection rates.

### 2.2 Real Time Signal and Image Processing Systems

Signal and image processing are very popular application domains of compute systems. The real time constraints that these domains usually pose, result in stringent system specifications. These specifications are often met with application specific architectures the accelerate parts or even complete digital signal processing algorithms. As a result, signal and image processing have sustained interest in real time response implementations by accelerating their computations. Finite Input Response (FIR) filter acceleration, for example, has been presented in [24] and [25]. Image processing acceleration, on the other hand, is becoming increasingly more complex due to the continuously increasing image resolutions used in vision systems. This results in even more stringent requirements, in terms of buffer memory and workload, that have to be met in order to achieve real time operation.

Image, and signal processing algorithms usually include multiplications with tunable parameters and a signal input (i.e. kernel window and image). These parameters have been traditionally defined by experts and involve signifiant human intervention. The emergence of ML has provided the means to define these parameters empirically, through the availability of datasets and without the need of expert knowledge. In addition, the automated training frameworks in the ML domain reduce human interaction to the minimum while yielding models that are competitive and often surpass algorithms defined by experts.

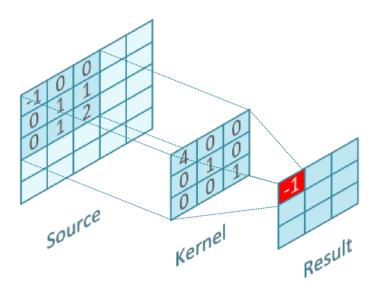

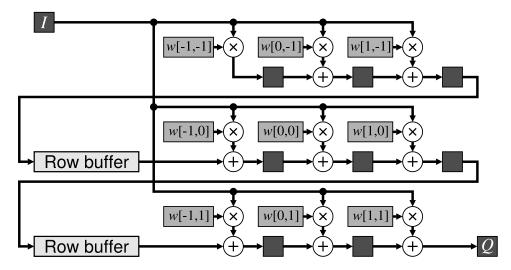

### 2.2.1 Convolution

Convolution, or 2-D spatial filtering, is fundamental operation in image processing. It comprises a kernel matrix, or filter window, that scans an input image at a given stride. During the scan, an output image pixel is generated by calculating the weighted sum of the overlapping kernel area, as depicted in Figure 2.1. The kernel dimensions and coefficients define the transformation of the image. For example the transformation can be edge detection, sharpening or even a specific feature in the image. Convolution has always been popular among the research community as it constitutes the foundation for many vision systems. Accelerating convolutions is therefore paramount for real time vision

Figure 2.1: Convolution operation showing the source image, overlapping kernel window and result image [26].

systems, as shown in [27–32]. Other previous work have approached this task alternatively, mainly divided into multiplierless, that make use various theorems, optimisations and transformations to avoid the use of multipliers [33–37], and others that make use of distinct multiplications [24, 25, 38].

### 2.3 Neural Networks

Neural Networks are computational models inspired by human cognition, able to form complex non-linear functions from a given dataset. Their learning, similarly to any other ML model, can be further categorised in supervised and unsupervised. In supervised learning, a dataset with a set of inputs and their corresponding outputs (i.e. labelled data) is provided. The Neural Network is then trained to match the expected output given that specific set of inputs, or classify them to a given class. During unsupervised training, a dataset with only inputs is provided, with the task to extract any patterns from the input data. For example, an unsupervised model could automatically cluster its input data to categories with similar features. Supervised learning therefore may include expert intervention to derive the output labels, rendering the preparation of the used dataset a more time-consuming process compare to unsupervised learning. On the other hand, unsupervised training requires more data and more time to achieve satisfactory accurate predictions, which in turn require more compute and memory resources during training. Lastly, unsupervised learning can also be susceptible to dataset artefacts or erroneous spikes that may have been included due to the automated operation of the process. As a result, most trained models used for benchmarking in the literature are trained

with supervised learning.

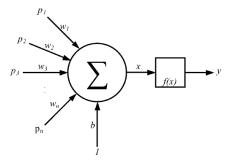

Figure 2.2: Neuron Structure, showing the inputs, weights, biases and activation function [12].

Neural Networks consist of compute entities called neurons, as shown in Figure 2.2. Each neuron calculates the weighted sum of its inputs, adds the result to an offset value (bias), followed by an activation function for non-linearity. Most commonly used activations functions are the Rectified Linear Unit (ReLU), sigmoid and tanh, as shown in equations 2.1 - 2.3.

$$relu(x) = max(0, x) \tag{2.1}$$

$$sigmoid(x) = \frac{1}{1 + e^{-x}} \tag{2.2}$$

$$tanh(x) = \frac{e^x - e^{-x}}{e^x + e^{-x}}$$

(2.3)

A layer is then formed with the use of multiple neurons, operating in parallel, and by extension, a Neural Network is built with a sequence of layers that propagate their results between them. The first layer of a Neural Network is the input layer, from which new data are fed to the network, whereas the last layer is the output layer, out of which the results of the network are generated. Any layers between the input and output layer are called hidden layers. Conventionally, Neural Networks with one or two hidden layers, in addition to the input and output layers, are called shallow. Networks with more than two hidden layers are considered deep networks. Various types of Neural Network layers exist that are tailored to different types on inputs. Depending on the layer type, the functionality of each neuron is somewhat different, however the core operation remains inherent. Neural Networks have been successfully applied in a broad range of fields, from automotive [39], to healthcare [7].

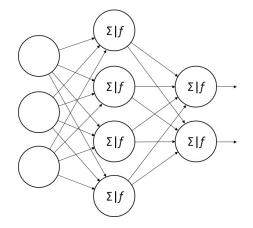

### 2.3.1 Fully Connected, or dense Layers

Fully connected, or dense, layers are the most commonly used type of layers as they can be used as an independent solution or be embedded in more complex Neural Network topologies. An indicative structure of a fully connected layer is shown in Figure 2.3. Inputs to fully connected layers are represented numerically and so symbolic (or categorical) inputs must be converted to suitable formats before being applied. Applications of NNs consisting solely of fully connected layers have been indicatively used in network security [12, 19, 20, 40, 41], healthcare [7], automotive [39], language processing [42] and gas classification [14].

Figure 2.3: Artificial neural network structure.

### 2.3.2 Convolutional layers-CNNs

Convolution gained even more attention in the recent years due to the success of Convolutional Neural Networks (CNNs) [43]. CNNs mainly consist of convolutional layers that use convolutions abundantly to extract features from an input image. Convolutional layer weights (i.e. kernel coefficients) are defined automatically during training. The correlation between convolution and CNNs is demonstrated in [37], in which the convolution operation in CNNs is optimised by using power of two weights.

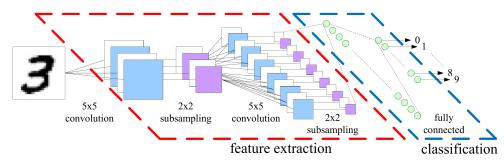

Convolutional layers incorporate the traditional 2-D convolution operation in image processing. Convolutions are more efficient at processing images compared to fully connected layers. For example, although an image could be flatted and used in a fully connected layer, it would require many more neurons and connections between them, resulting in higher memory and compute requirements. Convolutional layers act as feature extraction entities on the feature maps (i.e. images) that are propagated through the network. They are mostly used in tandem with other types of layers that perform the actual classification task on the extracted features. An example of a complete CNN is shown in Figure 2.4, which is trained for handwritten digit recognition [44]. The input images initially propagate through the feature extraction layers, that mainly consist of convolutional layers, followed by the classification part that consists of fully connected layers. Various CNN topologies have been proposed over the years, for example AlexNet[8], VGG [45] and GoogLeNet [46]. Each of these CNNs has pushed the state of the art while demonstrating improvements or tradeoffs between them. For example, a CNN topology may offer faster training turnaround, going deeper or reduce the overall workload, among others.

Figure 2.4: A typical CNN structure, showing the distinct feature extraction and classification parts [44].

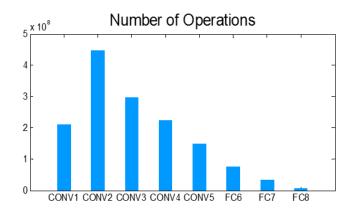

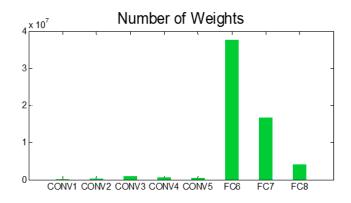

The different layers in a CNN have significantly different workload and memory requirements. Indicatively, the analysis that takes place in [13] extracts the number of operations, Figure 2.5, and the number of weights, Figure 2.6, for each layer. In this case, the convolutional layers comprise the largest workload while benefiting from weight reuse, whereas fully connected layers have reduced workload but higher memory requirements.

Figure 2.5: Per layer number of operations in AlexNet [13].

Figure 2.6: Per layer number of weights in AlexNet [13].

As a result of their popularity, toolflows have been proposed to map these CNN topologies on custom computing architectures [47]. In addition, although CNNs are primarily used for image recognition tasks, the work in [23] uses CNN topologies for a network security application. The authors have converted the network traffic features into images which have been used to train CNN networks. The proposed method however did not obtain better detection rate compared to simpler NNs comprising fully connected layers. Nonetheless, it demonstrates the versatility of neural networks in a broad range of domains.

### 2.3.3 Recurrent Layers-RNNs

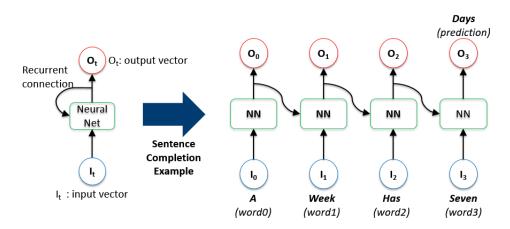

Figure 2.7: A recurrent unit, its unrolled computation over timesteps [48].

Recurrent layers are tailored for sequential or time series data applications. To enable this class of networks to extract any correlation between data sequences, they include feedback connections to previous outputs, which in turn translate to computing dependencies during their runtime. The feedback connections embed a memory element to the network, based on the data that has been previously propagated through the layer. An example of a recurrent unit unrolled over time is shown in Figure 2.7. The unit receives the first four words of a sentence serially and generates the fifth word, based on the previous ones. The initial structure of recurrent units however has been proven prone to vanishing and exploding gradients. The former case is when a gradient is very small, during training, and it continues to become smaller until it vanishes. The latter case is the exact opposite, referring to a gradient that is very big, creating an unstable model. As a result, variants have been proposed to overcome the aforementioned issues.

#### Long Short-Term Memory (LSTM) layers

Long Short-Term Memory (LSTM) and Gated Recurrent Units (GRUs) are RNNs that have been proposed to overcome the vanishing and exploding gradient problems. Although both perform similarly in many tasks, the more complex structure of LSTMs theoretically allows them to learn more complex sequential patterns.

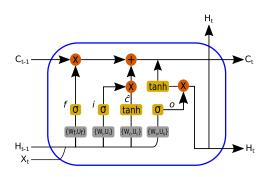

Figure 2.8: An LSTM unit.

Equations 2.4 to 2.9 describe the operation of an LSTM unit, which is also illustrated in Figure 2.8, where  $\odot$  denotes element-wise multiplication, and W and U are the weights of current input features and the previous cell outputs respectively. More specifically, an LSTM unit consists of the forget gate  $(f_t)$ , input gate  $(i_t)$ , and output gate  $(o_t)$ , along with the cell state $(C_t)$ , its partial result $(\tilde{C}_t)$ , and the LSTM cell output  $(H_t)$ . The forget gate controls the amount of information to discard from the previous cell state, the input and partial cell state define the new information to add to the cell state and the output gate defines the LSTM cell's output based on the current cell state. The main difference between LSTMs, and RNNs in general, and feedforward NNs, is the feedback connections from previous outputs  $(C_{t-1} \text{ and } H_{t-1})$ .

An LSTM network can process a sequence of inputs, each of which can be a scalar or a vector. The sigmoid ( $\sigma$ ) and tanh activation functions are most commonly used in this configuration. However, some flexibility in the application of activation functions is required to support different networks.

$$f_t = \sigma(W_f x_t + U_f H_{t-1} + b_f)$$

(2.4)

$$i_t = \sigma(W_i x_t + U_i H_{t-1} + b_i)$$

(2.5)

$$\tilde{C}_t = tanh(W_c x_t + U_c H_{t-1} + b_c)$$

(2.6)

$$o_t = \sigma(W_o x_t + U_o H_{t-1} + b_o)$$

(2.7)

$$C_t = f_t \odot C_{t-1} + i_t \odot \tilde{C}_t \tag{2.8}$$

$$H_t = tanh(c_t) \odot o_t \tag{2.9}$$

LSTMs have been successfully applied to weather forecast [49], network security [21, 22], optical character recognition [50, 51], speech recognition [52], character level text prediction [53–55], among others.

### 2.3.4 Hyperparameters and Evaluation

Hyperparameters are a set of parameters used during the training of a Neural Network that have an impact on how effectively the model learns from the input data. These parameters are usually defined experimentally as their impact differentiates according to the task at hand.

- Neurons per layer and number of layers: the number of neurons in a layer and the number of layers affect the learning capacity of the network. Therefore, depending on the complexity of the task at hand, different network topologies are explored to find the better suited one.

- Batch size: is the number of input samples after which the model coefficients (i.e. weights and biases) are updated during training.

- **Epochs:** an epoch is called after all samples in the training set have been propagated through the network once. Usually this process is repeated multiple times for the network to learn.

- Learning Rate: is the rate at which the coefficients are updated after the pass of a batch.

- Loss function: is the function with which the prediction error of a Neural Network is evaluated, which in turn affects the coefficient update during training.

- **Optimiser:** is the function, or algorithm, used to update the network's coefficients and reduce the prediction error of the model to ideally reach to the global minimum.

A Neural Network is frequently evaluated during training, e.g. after the pass of an epoch, showing the prediction error and, where possible, the percentage of correct classifications made. Although other metrics exist as well, accuracy is the most widely used one since it encapsulates the overall prediction capability of the model, while others focus on a specific attribute. For example, given a network that classifies its input data to two classes, e.g. class 1 and class 2, classification accuracy is calculated as follows:

$$accuracy = 100 * \frac{TP + TN}{TP + TN + FP + FN}$$

(2.10)

where:

- **TP**: True Positive, corresponds to a class 1 dataset entry has been correctly classified as such.

- **TN:** True Negative, corresponds to a class 2 dataset entry that has been correctly classified as such.

- **FP**: False Positive, corresponds to a class 1 dataset entry that has been incorrectly classified as class 2.

- **FN:** False Negative, corresponds to a class 2 dataset entry that has been incorrectly classified as class 1.

### 2.4 Compute Platforms

Compute platforms are the means by which Neural Networks are processed. These may be generic software programmable architectures, e.g. a Central Processing Unit (CPU) or a custom computing architecture implemented on an ASIC or FPGA.

### 2.4.1 Software Programmable Platforms

Software programmable platforms, CPUs and GPUs, have been the most popular for Neural Network computations. The ease of compiling an algorithm in software, coupled with the highly parallel operation of GPUs have rendered these platforms very user friendly. In addition, the availability Neural Network frameworks (e.g. Tensorflow [56], Keras [57], Caffe [58], Theano [59]), which have abstracted the low level details of NN implementations in software, acted as a catalyst for the wider use of these platforms.

#### Central Processing Units (CPUs)

The ubiquity of generic CPU compute architectures coupled with their low cost have rendered this class of units very appealing for NN execution. CPU capabilities may vary significantly in respect to the compute platform they are used in. For example, server CPUs are more capable compared to personal computer CPUs, both of which are more powerful compared to an embedded microprocessor that implements a Reduced Instruction Set Computing (RISC) architecture. Nonetheless, since embedded processors comprise the majority of edge devices' CPUs, there have been particular efforts in enabling a more efficient deployment to these devices through the use of compute optimisations. For example, Tensorflow [56] provides a *Lite* version that offers a range of optimisations for embedded processors, like the ARM Cortex-A72 on a Raspberry Pi 4.

Although the spectrum of CPU capabilities varies significantly depending on the targetted device, CPUs in general are not able exploit parallelism in NNs at significant extend due to their relevantly low core count and inefficiency in memory intensive computations. The work in [60] has shown that fully connected layer processing can become less efficient on CPUs due to their memory intensive patterns. This was demonstrated in an analysis conducted on AlexNet [8], a specific CNN topology. Two Intel Xeon E5-2650 CPUs running at 2.4GHz were used to measure AlexNet's Instructions Per Cycle rate (IPC). Fully connected layers achieved the lowest, compared to the other layer types, obtaining an IPC rate of less than 1, due to cache misses in all cache levels, causing a high number of stall cycles to fetch data from memory. Hence, we see that data flow optimisations are also important to fully reach the processing potential of the computing unit.

Therefore, despite the wide availability and ease of Neural Network deployment, CPUs are less likely to offer real time execution while also being less energy efficient for such tasks. As a result, latest CPU models include special NN processing units [61, 62], to offer more efficient processing for this class of algorithms.

### Graphic Processing Units (GPUs)

GPUs attracted significant interest in the NN domain on both, training and inference ends. Their highly parallel compute architecture coupled with the availability of an abstracted Application Programming Interface (API), for example Nvidia's Compute Unified Device Architecture (CUDA), have greatly reduced execution times on both training and inference while maintaining the ease of software programmability. GPUs form factor has diversified over the years, providing solutions that range from powerful GPUs for central computing

to GPUs in the embedded domain. Although Neural Networks' training is dominated, at the moment, by the use of powerful GPUs in workstations, the use of GPUs for inference, especially in the embedded domain, has not been very beneficial in terms of performance and efficiency, compared to custom computing architectures on ASICs and FPGAs. The latter is mainly due to the fact that custom computing architectures are more tailored to a specific application domain compared to the more generic architecture of GPUs. For example, GPUs offer limited parallelism in LSTMs due to their sequential components and dependencies to previous outputs. Therefore being underutilised when processing in streaming mode, requiring batch processing to achieve high throughput. Previous work in [52] showed that an LSTM implementation for speech recognition, that operates at 100MHz on a Xilinx Zynq XC7Z045 FPGA, is more energy efficient compared to a high-end NVIDIA GeForce Titan X GPU. The authors in [63] explored the partitioning and execution of large LSTM layers on FPGAs. Their proposed approach on a Xilinx Virtex 7 and a Zyng FPGAs demonstrated improved performance and energy efficiency compared to an Nvidia TITAN X Pascal GPU, in addition to a Intel Xeon E5-2665 CPU and previous work on FPGAs. The work in [55] proposed LSTM co-processors on Xilinx Zynq ZC7020, obtaining improved runtime and energy efficiency compare to an Nvidia Tegra TK1 GPU.

### 2.4.2 Application Specific Integrated Circuits (ASICs)

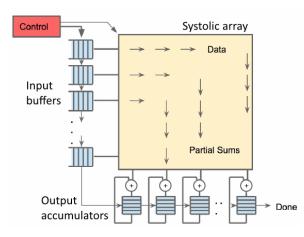

Application Specific Integrated Circuits (ASICs) have demonstrated superior performance and energy efficiency at the cost of flexibility. As reported in Chapter 1, FPGAs tradeoff between performance, flexibility and off-the-shelf availability have been the main advantages over ASICs. In addition, as Machine Learning is an actively explored domain, constantly pushing the state of the art, means that long fabrication times are likely to render ASICs outdated by the time they are produced. As a result, ASICs implementations in this domain are shown to maintain some flexibility with more generic architectures, for example, the systolic array architecture found in the Google TPU devices. As shown in Figure 2.9, the input data in a TPU systolic array flow from the left hand side, while the weights are loaded from the top. Compute units in between calculate partial sums which are accumulated at the lower end of the array.

Figure 2.9: Systolic Array dataflow used in Google Edge TPU [64].

A systolic array implementation would therefore require a number of external memory channels to provide the required input and weights bandwidth. Its compute unit arrangement makes it efficient for matrix-matrix multiplications, which is ideal for CNNs that are inherently tailored for batch inference, but not very efficient in operations of other network types, e.g. matrix-vector or vector-vector. Therefore, in streaming processing, systolic arrays would be less efficiently utilised due to the lack of batching and shared weights. Moreover, the fixed architecture of an ASIC systolic array means that their efficiency is heavily based on the Neural Network's dimensions, with small networks to underutilise its compute resources. Additionally, the dependencies in LSTMs make it very difficult to utilise the pipeline parallelism in this class of architectures due to their more regular dataflow.

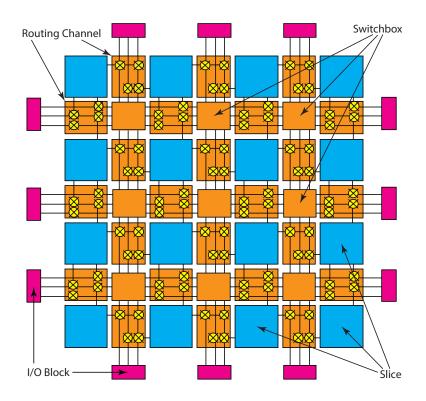

### 2.4.3 Field-Programmable Gate Arrays (FPGAs)

FPGAs are reconfigurable integrated circuits that can be found on various form factors that range from the embedded domain to high performance central computing. Their inner structure, depicted in Figure 2.10, comprises of a finite number of flexible routing resources and Configurable Logic Blocks (CLBs), or slices. Each CLB consists of small number of Look-Up-Table (LUT) memories, that can be used to implement any logic function, and synchronous memory elements, Flip-Flops (FFs). Each CLB is interfaced with a routing channel, which can be configured to I/Os of the CLB to the programmable interconnect. Routing channels are in turn interfaced with switchboxes which are able to make a connection between the available routing channels. FPGAs have evolved over the years to not only provide more configurable elements, but to also include hard macro blocks and interconnect for widely used operations, implemented directly in silicon. These macro blocks have enabled more efficient implementations, in terms of both performance and energy, while their dynamic

Figure 2.10: A part of an FPGA architecture, showing the various building blocks. [65].

programmability provides a degree of flexibility. Moreover, the reconfigurable fabric has also been integrated alongside an embedded processor, offering a complete system solution on an FPGA SoC. Depending on the family, the capabilities of FPGAs may vary, providing different interconnect capabilities, different number of macro blocks or more advanced LUT functionality, among others.

FPGAs have traditionally been used to accommodate custom computing architectures to accelerate workloads and achieve real time performance. Critical applications that require real time performance, among others, are network security algorithms. The faster the response in this class of algorithms means that less malicious packets enter the network, which results in a more effective defence mechanism. Accelerating traditional intrusion detection workloads on FPGAs has been explored in [66] and [67], while more modern ML approaches on FPGAs have been explored in [68–70]. In a similar way, FPGAs have also been used to accelerate vision computations for real time performance [28–32].

#### FPGA Macro blocks

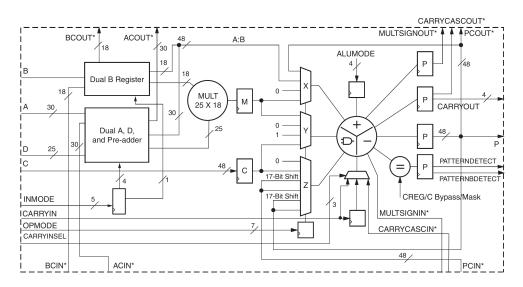

Figure 2.11: DSP48E1 compute block architecture, showing the various datapaths, compute units and configurations [71].

Hard macro blocks are distributed on the FPGA IC and can offer, for example, improved distributed memory storage, in the form Block RAM or most recently Ultra RAM, or advanced compute capabilities, with Digital Signal Processing (DSP) blocks. An average BRAM memory block has about 32 Kbit of memory which can be configured as  $32K \times 1$  bit,  $16K \times 2$  bit, etc. DSP blocks are able to perform more complex computations, that are widely used in signal processing applications. An indicative DSP block architecture is shown in Figure 2.11. It consists of three main compute blocks, a pre-adder, a multiplier and an Arithmetic Logic Unit (ALU). The operation of DSP blocks can be dynamically configured at runtime, for example, to execute various ALU operations or select the different input registers to the ALU. Thus providing some degree of flexibility through programmability.

#### FPGA SoCs

FPGA SoCs provide a complete system solution, featuring an embedded microprocessor tightly coupled with an FPGA on the same IC, as shown in Figure 2.12. These devices are therefore ideal for edge computing, combining the high-level management functionality of embedded processors with the compute acceleration of a custom architecture on an FPGA. The embedded microprocessor can not only be used for light computing but to also configure and control the FPGA dynamically after deployment. Many previous work implementing co-processors for Neural Networks on FPGAs have targetted SoC platforms in a manner that the microprocessor manages the data transfer, control and runtime coordination [53–55, 72]. Others have implemented

Figure 2.12: FPGA SoC architecture showing the reconfigurable fabric along with a microprocessor [65].

complete compute architectures on the FPGA fabric, benefiting from all the advantages of custom compute architecture, while leaving the microprocessor free and potentially deal with other tasks [73].

## 2.5 Compute Optimisations

Neural Networks' ubiquity has led to a significant interest in optimising this class of algorithms for more efficient processing. Previous work in the literature has analysed NN models and shown that they are typically over-parametrised, thus incorporating significant redundancy. Various compute optimisations have been explored, described in the following subsections, as a result of this observation, that aim for a more efficient use of compute and memory resources.

#### 2.5.1 Scheduling - Batch Inference

NNs are typically demanding in terms of workload and memory bandwidth. Even lightweight networks are typically too large to be fully unrolled on the compute units of embedded custom compute architectures or fit in their on-chip memories. Generic and custom compute architectures may therefore employ more complex scheduling techniques in order to make these computations more efficient in terms of compute resources utilisation and memory transfers [50, 63]. The most popular technique to process these networks is in batches, i.e. on a group of inputs rather than one input at a time. Similarly to the batch size hyperparameter during training. Specifically, a large NN is usually partitioned according to the capabilities of the targetted compute unit. Each partition weights are cached to the compute unit and computations take place for a

number of inputs, generating partial results of the NN. Consequently, the following partition is loaded and cached to the compute unit, calculating its own partial results based on the previously generated ones. This process is repeated until the whole Neural Network is processed. Batch processing in essence alleviates the overheads of loading weights for each input inference and is ideal when there are huge volumes of stored data. This method is very useful to accelerators with high speed PCIe interconnect (i.e. GPUs), in which the high transfer bandwidth is constantly filled with the available stored data. The availability of data in GPUs is paramount since these devices need to cache adequate data in their local memories to keep their compute cores occupied, and maintain high throughput. Otherwise, the available compute cores will be underutilised, resulting in poor performance and efficiency. Batch processing, however, is not always suitable for real time processing with streaming flow of data, e.g. data collected from a sensor on an edge device. The latter calls for custom compute architectures that are tailored to a streaming dataflow, making arrangements accordingly to be more efficient.

#### 2.5.2 Pruning

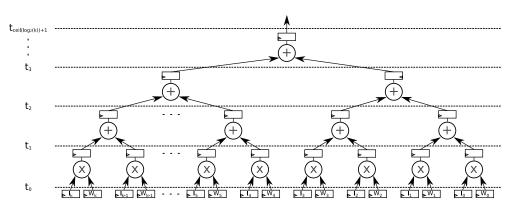

Figure 2.13: Pruned Neural Network example, showing weight (synapse) and neuron pruning [74].