## High-Level FPGA Accelerator Design for Structured-Mesh-Based Numerical Solvers

by

#### Kamalavasan Kamalakkannan

#### Thesis

Submitted to the University of Warwick

for the degree of

Doctor of Philosophy in Computer Science

### Department of Computer Science

April 2023

## Contents

| Conter           | its      |                                               | iii  |

|------------------|----------|-----------------------------------------------|------|

| Acknow           | wledger  | nent                                          | iv   |

| Declar           | ations   |                                               | v    |

| ${f Abstra}$     | ct       |                                               | vii  |

| Abbre            | viations | 3                                             | viii |

| $\mathbf{Symbo}$ | ls       |                                               | x    |

| List of          | Algori   | thms                                          | xii  |

| List of          | Figure   | $\mathbf{s}$                                  | xiii |

| List of          | Tables   |                                               | xv   |

| Chapte           | er 1 In  | ntroduction                                   | 1    |

| 1.1              | Contrib  | outions                                       | . 3  |

| 1.2              | Thesis   | Overview                                      | . 4  |

| Chapte           | er 2 B   | ackground                                     | 6    |

| 2.1              | FPGA     | Accelerator Device and Eco-System             | . 6  |

|                  | 2.1.1    | FPGA Accelerator Device Overview              | . 6  |

|                  | 2.1.2    | FPGA Programming                              | . 8  |

|                  | 2.1.3    | Loop Latency Estimation                       | . 10 |

| 2.2              | Structu  | ured Mesh-Based Numerical Schemes             | . 11 |

|                  | 2.2.1    | Explicit Schemes - Stencil Solvers            | . 12 |

|                  | 2.2.2    | Explicit Schemes - Related Work on FPGAs      | . 13 |

|                  | 2.2.3    | Implicit Schemes                              | . 15 |

|                  |          | 2.2.3.1 Alternating Direction Implicit method | . 16 |

|                  |          | 2.2.3.2 Tridiagonal solver algorithms         | . 18 |

|                  | 2.2.4    | Implicit Scheme - Related work on FPGAs       | . 20 |

| oter 3 Explicit Solvers on FPGAs                        | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 Accelerator Design for Stencil Computation            | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.1.1 Stencil Loop Transformation                       | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.1.2 Vectorization and Unrolling the Iterative Loop    | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.1.3 Decoupled Kernel Pipeline                         | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.1.4 Data Layout for Vector Elements                   | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2 Model for Baseline Design                             | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3 Optimizations                                         | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.3.1 Spatial and Temporal Blocking                     | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.3.2 Spatially Blocked Design using Multiple HBM Ports | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.3.3 Batching                                          | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4 Performance                                           | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.4.1 Poisson-5pt-2D                                    | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.4.2 Jacobi-7pt-3D                                     | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.4.3 Reverse Time Migration (RTM) - Forward Pass       | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5 Concluding Remarks and Discussion                     | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| oter 4 Implicit Schemes on FPGAs                        | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <del>-</del>                                            | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| _                                                       | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Ţ                                                       | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Performance                                             | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                         | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                         | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                         | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4 Concluding Remarks                                    | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| oter 5 FPGA Designs with SYCL                           | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                         | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                         | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                         | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                         | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C                                                       | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                         | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                         | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5 Concluding Remarks                                    | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ster 6 Towards Automating FDC A Designs                 | <b>7</b> 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                         | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                         | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                         | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                         | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1 2 3 4 D 1 2 3 4 D 1                                   | Accelerator Design for Stencil Computation 3.1.1 Stencil Loop Transformation 3.1.2 Vectorization and Unrolling the Iterative Loop 3.1.3 Decoupled Kernel Pipeline 3.1.4 Data Layout for Vector Elements Model for Baseline Design Optimizations 3.3.1 Spatial and Temporal Blocking 3.3.2 Spatially Blocked Design using Multiple HBM Ports 3.3.3 Batching Performance 3.4.1 Poisson-5pt-2D 3.4.2 Jacobi-7pt-3D 3.4.3 Reverse Time Migration (RTM) - Forward Pass Concluding Remarks and Discussion  ter 4 Implicit Schemes on FPGAs FPGA Design 4.1.1 Small and Medium System Solvers 4.1.2 Larger System Solvers Performance 4.2.1 ADI Heat Diffusion Application 4.2.2 Stochastic Local Volatility Discussion Concluding Remarks ter 5 FPGA Designs with SYCL Intel FPGAs and SYCL Stencil Solvers 5.2.1 Performance 5.4.1 Reverse Time Migration (RTM) Forward-Pass 5.4.2 ADI 2D Heat Diffusion Application 6.4.7 Reverse Time Migration (RTM) Forward-Pass 5.4.2 ADI 2D Heat Diffusion Application 6.5 Concluding Remarks  ter 6 Towards Automating FPGA Designs OPS Framework for Structured Mesh Applications 6.1.1 OPS API 6.1.2 Application Development Using OPS |

|        | 6.2.1  | ops_par_loop nodes: Skeleton For Baseline Design  | 89          |

|--------|--------|---------------------------------------------------|-------------|

|        | 6.2.2  | ops_par_loop nodes: Vectorization                 | 96          |

|        | 6.2.3  | ops_par_loop nodes: Batched Computation           | 98          |

|        | 6.2.4  | ops_par_loop nodes: Spatially Blocked Computation | 98          |

|        | 6.2.5  | Global Memory Access Nodes                        | 100         |

|        | 6.2.6  | Delay Buffers Nodes                               | 103         |

|        | 6.2.7  | ops_tridMultiDimBatch: Tridiagonal Solver Nodes   | 104         |

|        | 6.2.8  | Building Dataflow Graph                           | 106         |

| 6.3    | Optim  | al Design Parameter Identification                | 106         |

| 6.4    | Discus | ssion and Concluding Remarks                      | 109         |

| Chapte | er 7 C | Conclusions and Future Work                       | 111         |

| 7.1    | Contri | butions and Conclusions                           | 112         |

| 7.2    | Future | e Work                                            | 113         |

|        | 7.2.1  | Support for Larger Meshes                         | 113         |

|        | 7.2.2  | Support for Larger Number of Kernels              | 114         |

|        | 7.2.3  | DSL based Automatic Translator                    | 114         |

| Appen  | dix A  | 2D Heat diffusion using FDM                       | 126         |

| A.1    | FTCS   | - Explicit Numerical Scheme                       | 126         |

| A.2    | BTCS   | Numerical Scheme                                  | 127         |

| A.3    | ADI S  | cheme                                             | 127         |

| Appen  | dix B  | Performance of Implicit Applications on U50       | <b>12</b> 9 |

| B.1    | 2D AI  | OI Heat Diffusion Application                     | 129         |

| B.2    | 3D AI  | OI Heat Diffusion Application                     | 130         |

| B.3    | 2D AI  | OI Heat Diffusion Application on Larger Meshes    | 130         |

| B.4    | SLV A  | application                                       | 131         |

| Appen  | dix C  | Runtimes of Benchmarked Applications              | 132         |

| C.1    | Chapte | er 3 Runtimes                                     | 132         |

| C.2    | Chapte | er 4 Runtimes                                     | 135         |

| C 3    | Chapte | er 5 Runtimes                                     | 138         |

#### Acknowledgement

On this page, I want to convey my appreciation to the individuals and organizations who have provided assistance and inspiration in various ways during the course of this work. Their contributions have been invaluable, and without their help, this work would not have been possible. I am deeply grateful to them for the knowledge, exposure, and experience I have gained during my PhD.

First of all, I would like to thank my supervisors Dr. Gihan Mudalige and Dr. Suhaib Fahmy. Dr. Gihan offered me this fantastic PhD opportunity, being optimistic and flexible to my interests in research. I am thankful to Dr. Gihan not only for his academic guidance but also for being my go-to person for any kind of assistance, from visa applications to submitting my thesis. I appreciate the time and efforts Dr. Gihan dedicated to helping me develop various skills. Supervisor Dr. Suhaib helped me to dive into HLS-based FPGA acceleration and provided the Hardware and software resources necessary to undertake this research work. I express my gratitude to collaborator, Dr. Istvan Reguly, for providing valuable guidance on how to optimally implement applications on GPUs. I like to extend my thanks to my advisors Dr. Ligang He and Dr. Victor Sanchez for their valuable feedback on my progress during the PhD.

I would like to thank the department of computer science, university of Warwick for offering the funding for PhD and the Department of Engineering, Xilinx and Intel for offering the accelerator devices and software. I would like to thank Jacques Du Toit and Tim Schmielau at NAG UK Ltd for providing the C SLV application. I am thankful to John Shanly, Bogdan Pasca, Yohann Yugen for their support and flexibility during my internship at Intel UK.

It is a pleasure to acknowledge the support and friendship of many lab mates and colleagues including, Dr. Gabriele pergola, Dr. Ali Mohammadi Shanghooshabad, Dr. Arun prabhakar, Dr. Viswash Batra, Suneth Ekanayaka, Zaman Lantra, Archi Powell and Zhihao and Megdad kurmanji. I would like to mention friends, Natheesan, Gowtham Maran, Piradeef and Kokulraj for the valuable discussions, inspiration and support given during this work.

Finally, I am grateful to my parents and siblings for their unwavering support, encouragement and guidance throughout my life. My sister Kalaivarny sparked my interest in science through inspiring and motivational conversations. I want to convey my appreciation to my wife Arsitha for being a supportive and encouraging force in my personal and professional growth.

#### **Declarations**

This thesis is submitted to the University of Warwick in support of my application for the degree of Doctor of Philosophy in Computer Science. I, Kamalavasan Kamalakkannan, declare that this thesis titled, 'High-Level FPGA Accelarator Design for Structured-Mesh-Based Numerical Solvers' has been composed by myself and has not been submitted in any previous application for any degree. I confirm that:

- This work was done wholly or mainly while in candidature for the research degree at this University.

- The work presented (including data generated and data analysis) was carried out by the author.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

Portions of this work have appeared in the following publications:

- Parts of Chapter 3 in[33]:

Kamalavasan Kamalakkannan, Gihan R. Mudalige, Istvan Z. Reguly, and Suhaib A. Fahmy. 2021. High-Level FPGA Accelerator Design for Structured-Mesh-Based Explicit Numerical Solvers, 2021 IEEE International Parallel and Distributed Processing Symposium (IPDPS), Portland, OR, USA, 2021, pp. 1087-1096.

- Parts of Chapter 4 in[35]:

Kamalavasan Kamalakkannan, Gihan R. Mudalige, Istvan Z. Reguly, and Suhaib A.

Fahmy. 2022. High throughput multidimensional tridiagonal system solvers on FP-GAs. In Proceedings of the 36th ACM International Conference on Supercomputing (ICS '22). Association for Computing Machinery, New York, NY, USA, Article 19, 1–12.

- Parts of Chapter 5 in[34]:

Kamalavasan Kamalakkannan, Gihan R. Mudalige, Istvan Z. Reguly, and Suhaib

A. Fahmy. 2022. FPGA Acceleration of Structured-Mesh-Based Explicit and

Implicit Numerical Solvers using SYCL. In International Workshop on OpenCL (IWOCL'22). Association for Computing Machinery, New York, NY, USA, Article 19, 1–11.

The tridiagonal solver library and applications developed in this work are available as open-source software :

#### Git Repositories:

- StencilsOnFPGA[37] https://github.com/OP-DSL/StencilsOnFPGA Explicit stencil solver-based applications used for benchmarking Xilinx and Intel FPGAs with Nvidia V100 in Chapters 3 and 5

- Tridsolver-FPGA[36] https://github.com/OP-DSL/Tridsolver-FPGA

Batched Trisolver library for Xilinx and Intel FPGAs along with 2D and 3D ADI

applications used for benchmarking FPGAs with Nvidia-V100 GPU in Chapters 4

and 5

### Abstract

Field Programmable Gate Arrays (FPGAs) have become highly attractive as accelerators due to their low power consumption and re-programmability. However, a key limitation is the time and know-how required to program them. Even with high-level synthesis tools, they still require significant hand-tuned/low-level customizations and design space exploration to gain good performance. The need to program FPGAs using the data-flow programming model, much less well known and practised by the high-performance computing (HPC) community, is a major barrier for adoption for HPC.

The underlying motivation of this work is to bridge this gap - attaining near-optimal performance vs the ease of programming. To this end, we target the important class of applications based on structured meshes, focusing on numerical algorithms based on explicit and implicit techniques. We leverage the main characteristics of the application class, its computation-communication pattern and the hardware features. For explicit schemes, characterized by stencil computations, we unify the state-of-the-art techniques such as vectorization and unrolling with a number of new high-gain optimizations such as creating perfect data reuse data-paths, batching and tiling. A key new feature is their applicability to multiple stencil loops enabling the development of real-world workloads. For implicit schemes, we re-evaluate the characteristics of the tridiagonal system solver algorithms for FPGAs and develop a new high throughput batched multi-dimensional tridiagonal system solver library with orders of magnitude better performance than the state-of-the-art.

New analytic models are developed to support the solvers, elucidating and modelling the critical path of execution and parameterizing the design. This together with the optimal designs and new library lead to a unified design work-flow for synthesis on FPGAs.

The new workflow is used to implement a range of applications, from simple single stencil designs, multiple stencil loops to solvers with real-world utility. They are synthesized on the currently dominant Xilinx and Intel FPGAs. Benchmarking indicate the FPGAs matching or outperforming the best GPU implementations, the current best traditional architecture device solution. Over 30% energy saving can also be observed. The performance model demonstrates over 85% accuracy.

The thesis discusses the determinants for these applications to be amenable for FPGA implementation, providing insights into the feasibility and profitability of a design. Finally we propose initial steps in automating the workflow to be used through a DSL.

## Abbreviations

| ADI Alternating Direction Implicit           |

|----------------------------------------------|

| ALM Adaptive Logic Modules                   |

| ALU Arithmetic Logic Unit                    |

| AoS Array of Structure                       |

| API Application Programming Interface        |

| ASIC Application Specific Integrated Circuit |

| AXI Advanced eXtensible Interface            |

| BTCS Backward Time Centered Space            |

| CFD Computational Fluid Dynamics             |

| CGRA Coarse Grained Reconfigurable Arrays    |

| CPU Central Processing Unit                  |

| CUDA Compute Unified Device Architecture     |

| DDR4 Double Data Rate 4                      |

| DSL Domain Specific Language                 |

| <b>DSP</b> Digital Signal Processing         |

| FDM Finite Difference Method                 |

| <b>FEM</b> Finite Element Method             |

| FIFO First Input First Output                |

| FPGA Field Programmable Gate Array vii       |

| FTCS Forward Time Centered Space             |

| FVM Finite Volume Method                     |

| GPU Graphical Processing Unit                |

| HBM High Bandwidth Memory 32                 |

| HDL Hardware Description Language                       | 1 |

|---------------------------------------------------------|---|

| HLS High Level Synthesis                                | 1 |

| <b>HPC</b> High Performance Computing                   | 1 |

| ISL Iterative Stencil Loop                              | ŏ |

| <b>LUT</b> Look Up Table                                | 3 |

| MISD Multiple Instruction Multiple Data                 | 5 |

| OPS Oxford Parallel library for Structured mesh solvers | 5 |

| PCIe Peripheral Component Interconnect Express          | ) |

| PCR Parallel Cyclic Reduction                           | 3 |

| PDE Partial Differential Equation                       | 3 |

| QoR Quality of Results                                  | ) |

| RTM Reverse Time Migration                              | 9 |

| SIMT Single Instruction Multi Thread                    | 5 |

| SLR Super Logic Region                                  | 7 |

| SLV Stochastic-Local Volatility                         | 3 |

| SM Streaming Multi-Processor                            | 5 |

| SoA Structure of Arrays                                 | 7 |

| USM Unified Shared Memory                               | 3 |

## **Symbols**

B Batch size

Block<sub>valid</sub> Valid mesh point update in s spatial block

$BW_{channel}$  Off-chip memory channel Bandwidth  $Clks_{2D}$  Clock Cycles for 2D stencil computation  $Clks_{3D}$  Clock Cycles for 3D stencil computation

D Stencil Order

$delay_{2D}$  Total delay in number of clock cycles for 2D applica-

tion from input to output for single iteration

$delay_{3D}$  Total delay in number of clock cycles for 3D applica-

tion from input to output for single iteration

$FPGA_{dsp}$  Number of DSP units in FPGA

$FPGA_{mem}$  Available on-chip memory on FPGA

f Operating frequency of design implemented on FPGA

$f_u$  PCR inner loop unroll factor

g Number of Tri-diagonal systems interleaved for

thomas solver

$G_{dsp}$  Number of DSP units required to update single mesh

point

$l_f, l_b$  Arithmetic pipeline latency for forward and backward

loops

$l_{il}$  PCR inner loop pipeline latency

m, n, l Mesh Dimensions

N Tri-diagonal system size

$N_b$  Number of blocks in spike solver  $N_{CU}$  Number of Compute modules

$n_{iter}$  Number of Iterations

p Iterative loop unroll factor

$p_{dsp}$  Possible iterative loop unroll factor under DSP con-

straint

$p_{mem}$  Possible iterative loop unroll factor under onchip

memory constraint

t Tile size in Tiled Thomas solver

V Vectorization Factor

x,y,z system sizes in each dimensions, similar to m,n,l

# List of Algorithms

| 1 | $\mathtt{thomas}(a,b,c,d,u)$      | 19 |

|---|-----------------------------------|----|

| 2 | $\mathtt{pcr}(a,b,c,d,u)$         | 19 |

| 3 | RTM - Forward Pass                | 40 |

| 4 | 3D ADI Heat Application           | 51 |

| 5 | 2D Heston SLV Backward            | 59 |

| 6 | 2D ADI Heat Diffusion Application | 75 |

| 7 | 2D ADI Heat Diffusion Application | 86 |

| 8 | Baseline approach                 | 08 |

| 9 | Spatial blocking approach 1       | 09 |

# List of Figures

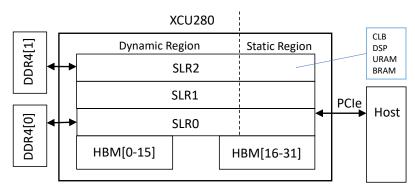

| 2.1  | Xilinx Alveo U280 FPGA accelerator device                                                                                                   |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|

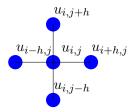

| 2.2  | Five-point stencil for 2D-Poisson equation                                                                                                  |

| 2.3  | Poisson stencil loop updates                                                                                                                |

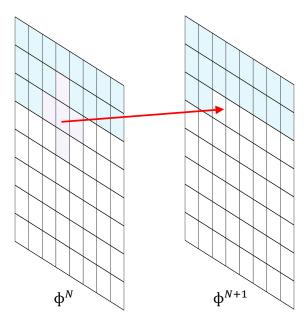

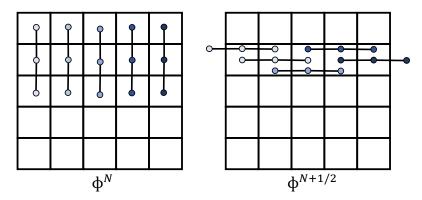

| 2.4  | Required mesh points for xsolve in step N and $N + \frac{1}{2}$                                                                             |

| 2.5  | After one iteration of PCR outer loop                                                                                                       |

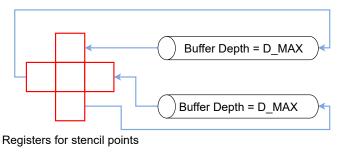

| 3.1  | Window buffer and factor of 2 vectorizations                                                                                                |

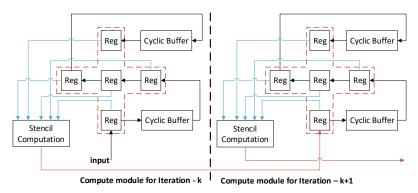

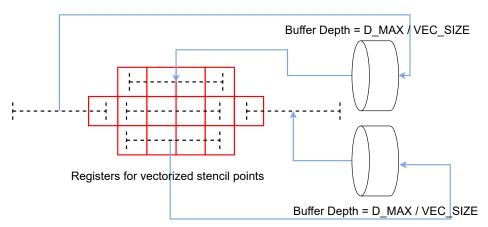

| 3.2  | Unrolling the iterative loop                                                                                                                |

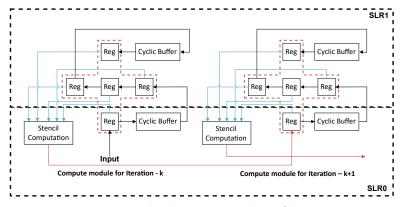

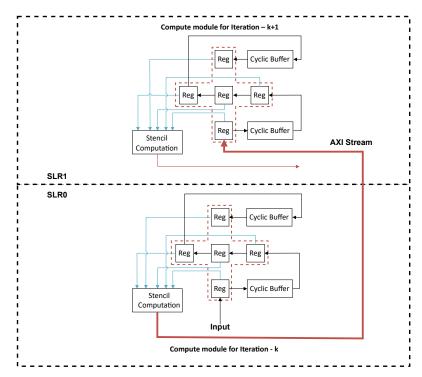

| 3.3  | Kernel placement without SLR constraint                                                                                                     |

| 3.4  | SLR constrained kernel placement                                                                                                            |

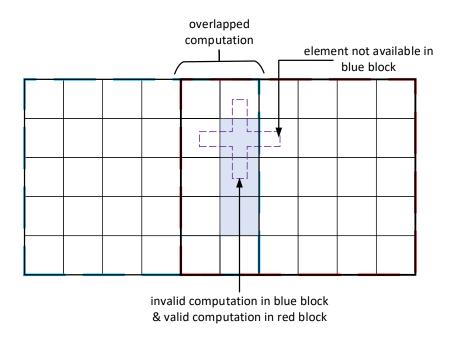

| 3.5  | Overlapped spatial blocks                                                                                                                   |

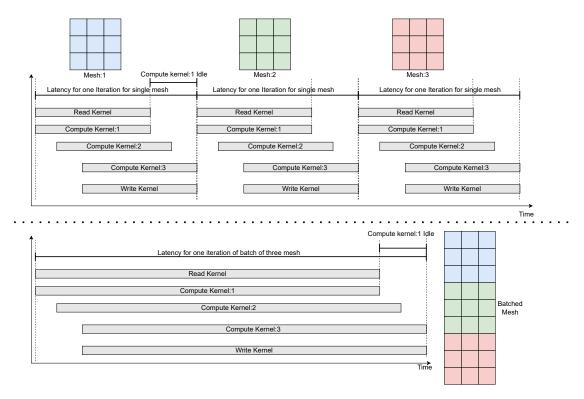

| 3.6  | Individual Vs Batched computation                                                                                                           |

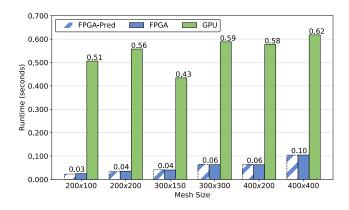

| 3.7  | Poisson-5pt-2D performance (Baseline - 60k iters)                                                                                           |

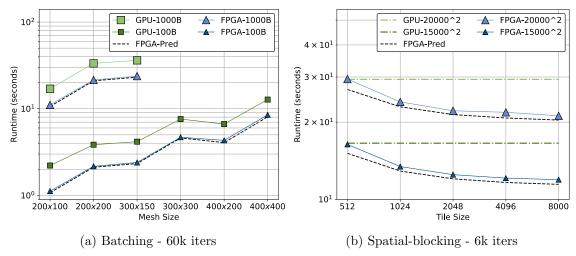

| 3.8  | Poisson-5pt-2D performance                                                                                                                  |

| 3.9  | Jacobi-7pt-3D performance (Baseline - 29k iters)                                                                                            |

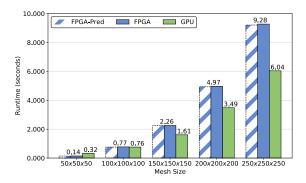

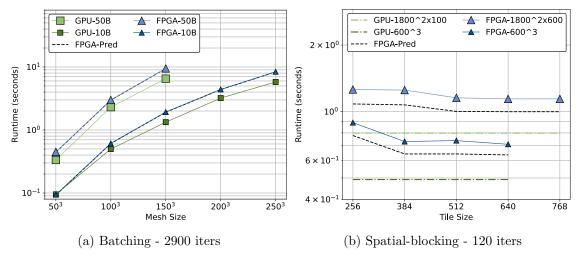

| 3.10 | Jacobi-7pt-3D performance                                                                                                                   |

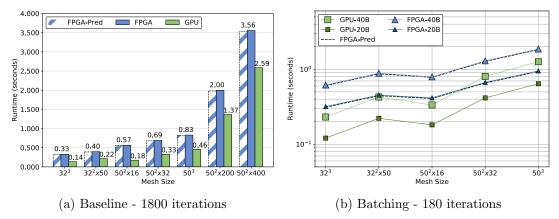

| 3.11 | RTM performance                                                                                                                             |

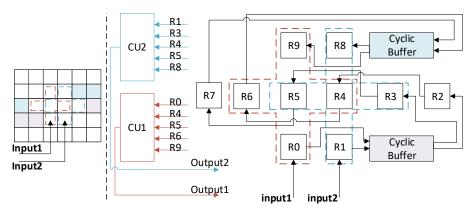

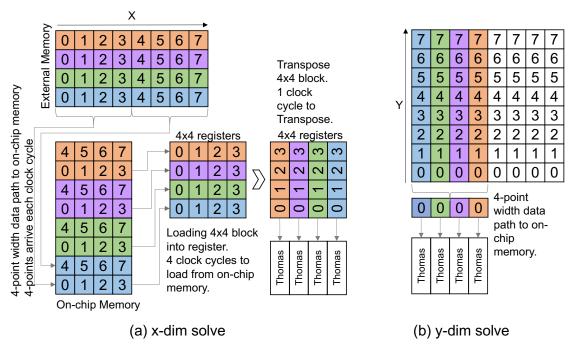

| 4.1  | Datapath for $4 \times$ (vectorized) $x$ - and $y$ -dim solves                                                                              |

| 4.2  | Reduced system formation                                                                                                                    |

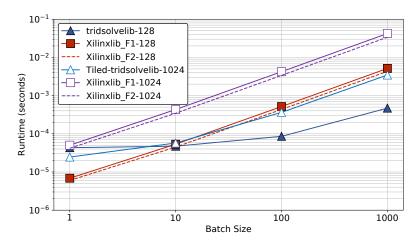

| 4.3  | Proposed tridsolvlib vs xilinxlib (FP32) performance for system sizes                                                                       |

|      | of 128 and 1024                                                                                                                             |

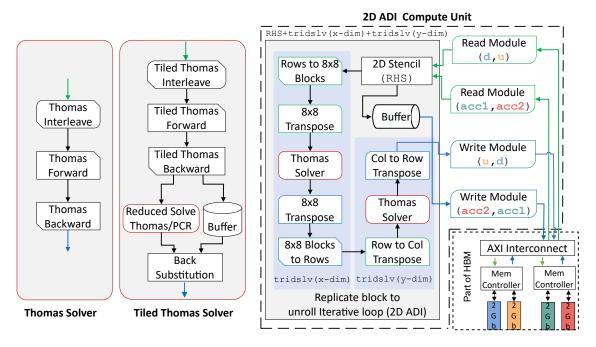

| 4.4  | 2D ADI application datapath constructed from solver components 53                                                                           |

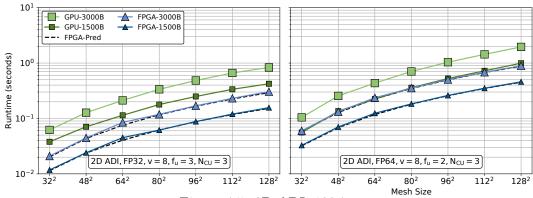

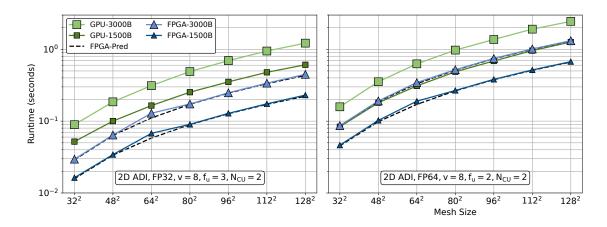

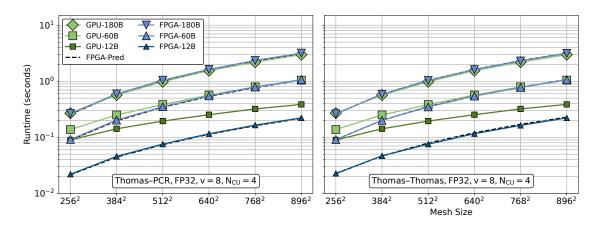

| 4.5  | 2D ADI: 120 iter                                                                                                                            |

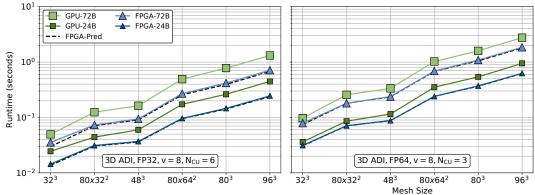

| 4.6  | 3D ADI:100 iter                                                                                                                             |

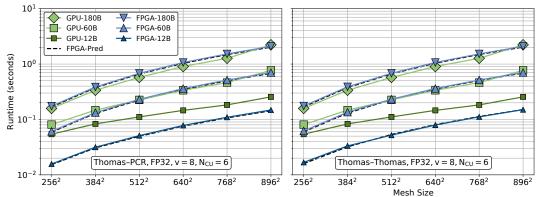

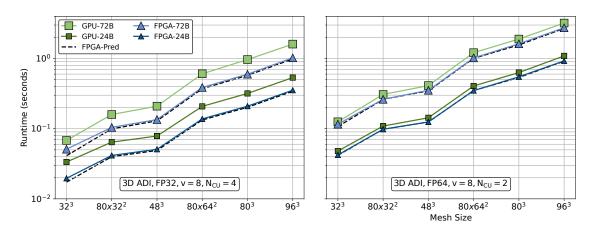

| 4.7  | 2D ADI-Tiled: 100 iter                                                                                                                      |

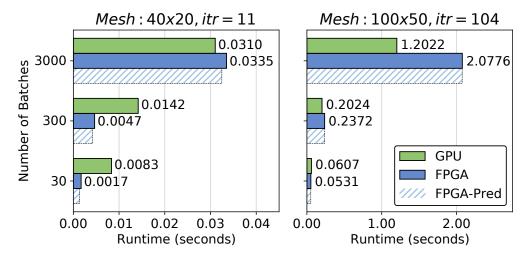

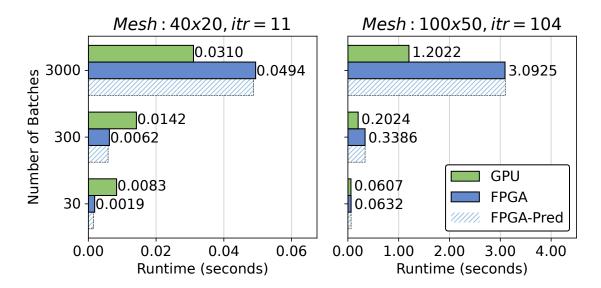

| 4.8  | SLV application performance                                                                                                                 |

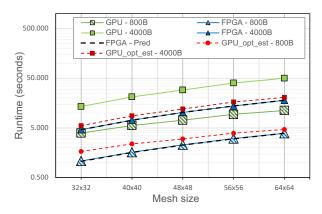

| 5.1  | RTM forward-pass, FP32, $p = 2, v = 3, 200$ iterations                                                                                      |

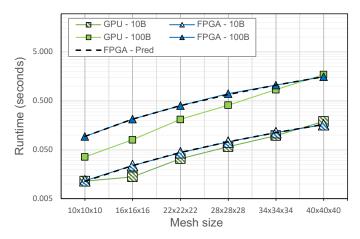

| 5.2  | ADI 2D, FP32, $f_U = 8, V = 8, 16000$ iter meshes                                                                                           |

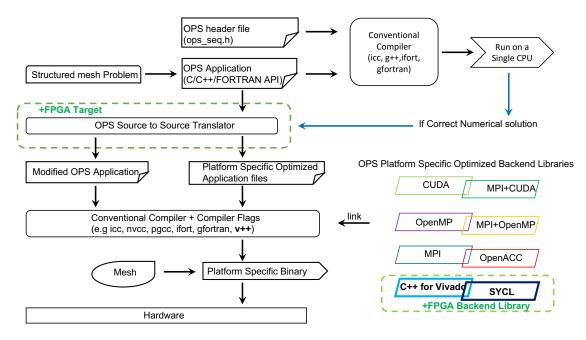

| 6.1  | The workflow for developing an application with OPS (based on [51]) and how the proposed new FPGA back-end will fit within the framework 85 |

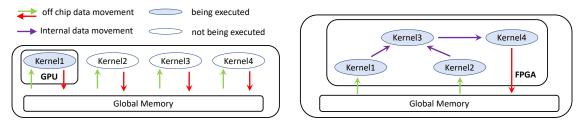

| 6.2 | kernel execution overview, classical accelerators Vs FPGA 85 |

|-----|--------------------------------------------------------------|

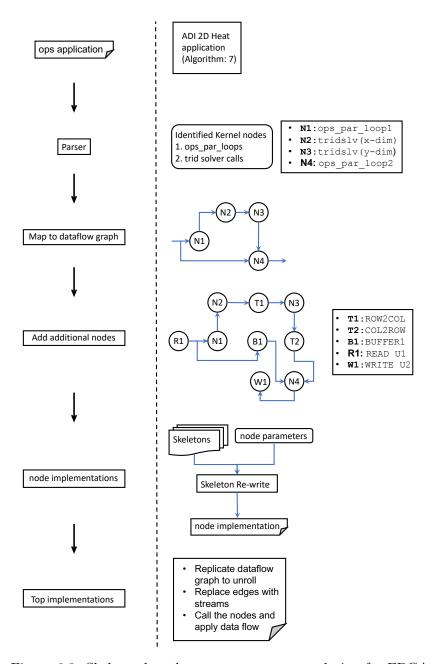

| 6.3 | Skeleton based source to source translation for FPGA         |

| 6.4 | Data path for vectored stencil computation                   |

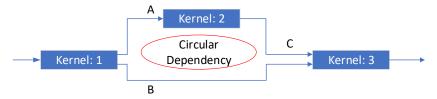

| 6.5 | Circular dependency on branches                              |

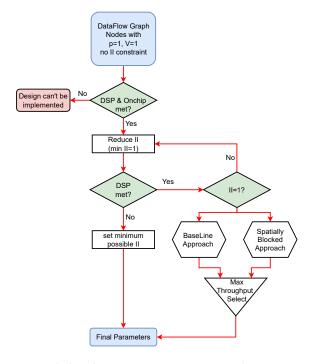

| 6.6 | High-level overview to estimate design parameters            |

|     |                                                              |

| B.1 | 120 iterations                                               |

| B.2 | 100 iterations                                               |

| В.3 | 100 iterations                                               |

| B.4 | SLV application                                              |

## List of Tables

| 3.1 | Experimental system's specifications                                     | 35 |

|-----|--------------------------------------------------------------------------|----|

| 3.2 | Model parameters for baseline and batched designs                        | 35 |

| 3.3 | Spatial blocking model parameters                                        | 36 |

| 3.4 | Poisson-5pt (Baseline and Batched, $60k$ iters) - Bandwidth (GB/s) and   |    |

|     | $\operatorname{Energy}(kJ). \ \ldots \ldots \ldots \ldots \ldots$        | 37 |

| 3.5 | Poisson-5pt (Spatial-blocking, 60k iters) - Bandwidth (GB/s) and En-     |    |

|     | $\operatorname{ergy}(kJ)$                                                | 38 |

| 3.6 | Jacobi-7pt-3D (Baseline and Batched): Bandwidth (GB/s) and Energy(kJ)    | 39 |

| 3.7 | Jacobi-7pt-3D (Spatial-blocking, 120 iters): Bandwidth (GB/s) and En-    |    |

|     | $\operatorname{ergy}(kJ)$                                                | 40 |

| 3.8 | RTM - Average Bandwidth (GB/s) and Energy(kJ) $\dots \dots \dots$        | 41 |

| 4.1 | Experimental systems specifications                                      | 51 |

| 4.2 | 2D ADI Heat Diffusion App. : Achieved Bandwidth (GB/s) and Energy        |    |

|     | (J) on the FPGA (F) and GPU(G)                                           | 54 |

| 4.3 | 3D ADI Heat Diffusion App. : Achieved Bandwidth (GB/s) and Energy (J) on |    |

|     | the FPGA (F) and GPU(G)                                                  | 57 |

| 4.4 | ADI Heat Diffusion App (2D FP32) – Large meshes, Thomas-PCR: 100         |    |

|     | iterations, Bandwidth (GB/s), Energy (J) on the FPGA (F) and GPU (G).    | 58 |

| 4.5 | SLV Application, Bandwidth (GB/s) and Energy (J)                         | 60 |

| 5.1 | Experimental systems specifications                                      | 73 |

| 5.2 | RTM - Avg. Bandwidth, $BW$ (GB/s), Avg. Utilisation(%) and Energy, $E$   |    |

|     | (J), 200 iters                                                           | 75 |

| 5.3 | ADI Heat Diffusion Application: Achieved Bandwidth, $BW$ (GB/s) Utili-   |    |

|     | sation(%) and Energy, $E$ (KJ)                                           | 77 |

| 6.1 | Stencil kernel parameters                                                | 89 |

| 6.2 | Spatially Blocked Design parameters                                      | 98 |

# List of Listings

| 1  | Sequential execution of for loop                 | 10  |

|----|--------------------------------------------------|-----|

| 2  | Pipelined loop body computation                  | 11  |

| 3  | A 2D flattened stencil loop                      | 24  |

| 4  | Transformed stencil loop                         | 25  |

| 5  | NDRange based stencil computation                | 64  |

| 6  | single_task based stencil computation            | 65  |

| 7  | Vectored stencil computation                     | 67  |

| 8  | Stencil compute kernel skeleton                  | 68  |

| 9  | Pipelining stencil compute kernels               | 68  |

| 10 | Global memory read-write loop                    | 69  |

| 11 | OPS block and datasets                           | 82  |

| 12 | A Stencil computation loop                       | 83  |

| 13 | Example OPS application                          | 84  |

| 14 | Skeleton for the baseline design                 | 90  |

| 15 | #pragma to select on chip memory block           | 92  |

| 16 | Mesh point index computation                     | 93  |

| 17 | Resource optimized mesh index computation        | 93  |

| 18 | Window buffer index computation                  | 94  |

| 19 | Window buffer implementation                     | 94  |

| 20 | Conditional FIFO pop                             | 95  |

| 21 | Stencil computation using values in the register | 95  |

| 22 | Conditional FIFO push                            | 96  |

| 23 | Wider data types                                 | 96  |

| 24 | Vectored stencil computation                     | 98  |

| 25 | Looping through spatial blocks                   | 99  |

| 26 | Memory interface configuration                   | 101 |

| 27 | Coalesced memory access                          | 102 |

| 28 | Tiled memory access                              | 103 |

| 29 | tridslv(x-dim) on FPGA                           | 105 |

| 30 | tridslv(y-dim) on FPGA                           | 105 |

| 31 | Dataflow optimization                            | 106 |

### Chapter 1

## Introduction

FPGAs have become highly attractive as accelerator architectures by virtue of their high performance, low power consumption, low latency in processing and re-programmability compared to Application Specific Integrated Circuit (ASIC) counterparts. As a result, FPGAs have gained a foothold in a wider range of application domains such as cyber security [13], databases [58], and deep learning [85]. In recent years, the integration of FPGAs as first-class accelerator platforms has also attracted significant interest in the High Performance Computing (HPC) and scientific computing communities, particularly in the financial computing domain [5]. They have also emerged as a potential accelerator platform for cloud computing [21]. However, a key limitation has been the design effort needed to produce performant accelerators for FPGAs, traditionally implemented through Hardware Description Language (HDL) such as Verilog and VHDL. Implementation of FPGA accelerators using HDL requires expertise in digital system design and optimizations. Moreover, HDL implementations usually require longer design and verification time.

Recent work [94, 59] and commercial FPGA vendors have attempted to address this problem with High Level Synthesis (HLS) tools that can translate programs written in standard high-level languages such as C/C++ or SYCL [73]/OpenCL [55] to a low-level HDL implementation. While this approach has improved the programmability of FP-GAs considerably they still require low-level customization and hand-tuning to produce design synthesis with optimum performance. Compared to programming traditional architectures such as CPUs or GPUs, the user has to build the memory hierarchy and data path using the supported high-level language constructs. Such data paths and algorithm transformations must be carefully carried out in order to gain performance on FPGAs as it comes with a fixed set of resources and its operating frequency is significantly lower compared to CPUs and GPUs. As such, getting good performance on FPGAs remains a challenging endeavour.

One solution to this problem is a domain-specific approach, leveraging the key characteristics of applications, their computation and communication patterns or motifs to explore the design space on the target accelerator device. Once the best optimization