# Depleted Monolithic Active Pixel Sensors (DMAPS)

## **Eva Vilella**

University of Liverpool

Department of Physics

Oliver Lodge Laboratory

Oxford Street

Liverpool L69 7ZE

vilella@hep.ph.liv.ac.uk

#### Who am I?

2013

2014 to 2019

2019

## PhD in Engineering and Advanced Technologies @ University of Barcelona

- Prototype detector for possible future linear colliders

- Application in medical devices

#### PDRA @ University of Liverpool

- New R&D programme to develop DMAPS for particle physics experiments

- Prototype detectors for ATLAS and Mu3e with international collaborations

- More generic developments with the CERN-RD50 collaboration

#### **UKRI Future Leaders Fellow @ University of Liverpool**

- R&D programme to develop highly performant DMAPS for future particle physics experiments

- Group leader of the Liverpool DMAPS R&D programme

- Member of several international collaborations (CERN-RD50, LHCb, etc.)

#### **Outline**

#### Silicon tracking detectors

- Sensor detection principle

- Readout electronics

#### Pixels

- Hybrids

- Monolithic Active Pixel Sensors MAPS

- Depleted Monolithic Active Pixel Sensors DMAPS

- Commercial vendors

- Low vs large fill-factor

#### DMAPS for particle physics

- Mu3e

- ATLAS ITk upgrade

- CERN-RD50

- Main design aspects

- Main evaluation results

#### Conclusion

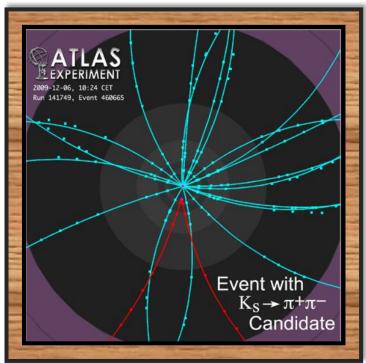

## **Particle tracking**

E. Vilella (Uni. Liverpool) – DMAPS seminar

## Silicon tracking detectors

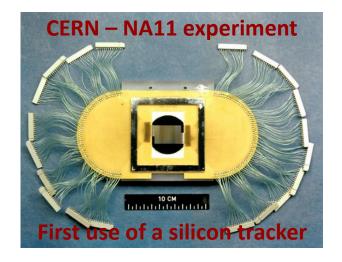

- Silicon tracking detectors have been used in particle physics experiments since the early 80's

- They introduced a significant improvement of the spatial resolution in comparison to that provided by state-of-the-art detectors at the time:

- Multi-wire proportional chambers (< 1 mm)</li>

- Drift chambers (~100 μm)

- Two main variants:

- Micro-strips (~10 μm spatial resolution)

- 100 channels/cm<sup>2</sup>

- Pixels (~10 μm spatial resolution)

- o 5000 channels/cm<sup>2</sup>

- True 3D reconstruction

- Capable to cope with high density and rate particle tracks

- Capable to survive harsh radiation environments

- → Close to the interaction point

**CERN** server

## **Sensor – Detection principle**

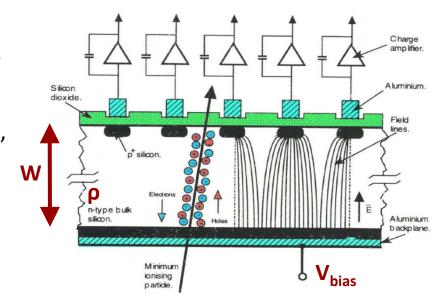

- Silicon p-n diode in reverse bias

- A traversing particle creates e<sup>-</sup>/h<sup>+</sup> pairs by ionization

- The electric field separates the e<sup>-</sup>/h<sup>+</sup> pairs, which move to the detector electrodes where they generate signal

- Basic requirements:

- Large bias voltage (V<sub>bias</sub>)

- Larger W → larger signal

- Faster charge collection

- Better radiation tolerance

- High resistivity silicon bulk (ρ)

- Backside biasing

- More uniform electric field lines

- Improved charge collection efficiency

- The signal is amplified, discriminated and digitized by the readout electronics

$$\rightarrow$$

W =  $\sqrt{\rho \cdot V_{bias}}$

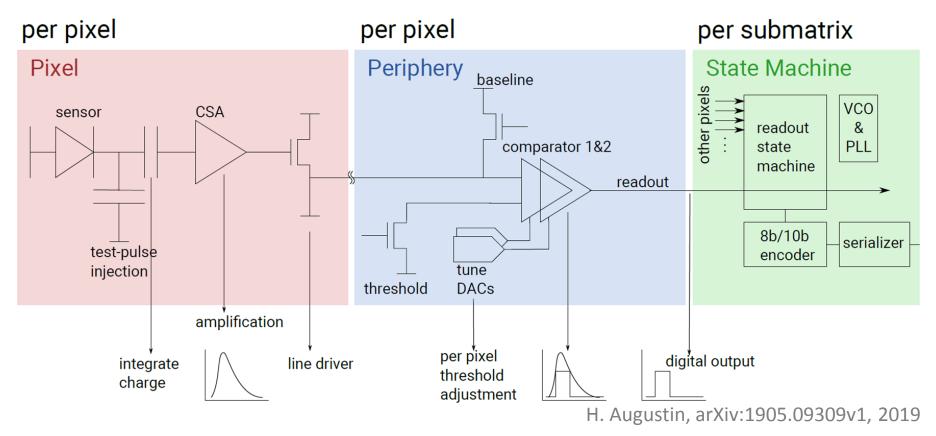

## Readout electronics – Block diagram

- Charge Sensitive Amplifier (CSA)

- Signal charge integration

- Pulse shaping (feedback capacitor with constant current)

- Comparator with DAC for local threshold voltage compensation

- Pulse digitization

- Length of digital pulse determined by time at which the rising and falling edges cross the comparator threshold voltage (Time over Threshold or ToT)

- RAM and ROM memories to store time-stamps and pixel address

- In deep sub-micron technologies for high density of integration

## **Hybrid pixel detectors**

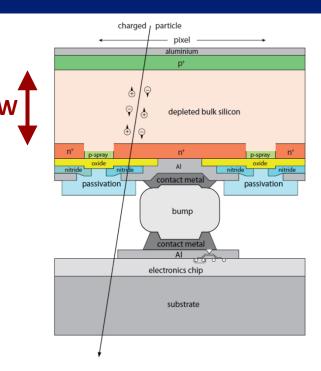

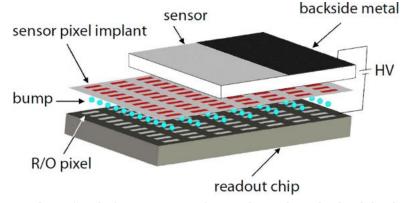

- Sensor and readout electronics on separate wafers

- Best technology for the sensor and the readout electronics

- Very fast charge collection by drift (1 ns)

- Fully depleted bulk (large signal)

- Radiation tolerant (10<sup>16</sup> 1MeV n<sub>eq</sub>/cm<sup>2</sup>)

- Capability to cope with high data rates

- 1-to-1 connection between sensor and readout chip via tiny conductive bumps using bumping and flipchip technology

- Limited pixel size (55 μm x 55 μm)

- Substantial material thickness (300 μm)

- Limited fabrication rate (bump-bonding and flip chipping is complex)

- Expensive (> £1M/m²) custom wafers and processing

- State-of-the-art for high rate experiments

M. Garcia-Sciveres, arXiv:1705.10150v3, 2018

## **Hybrid pixel detectors in HEP**

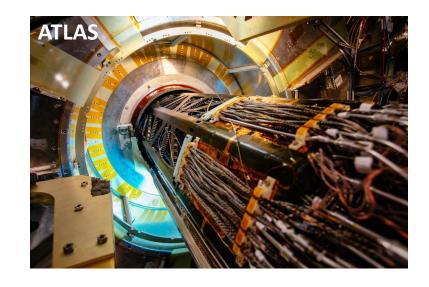

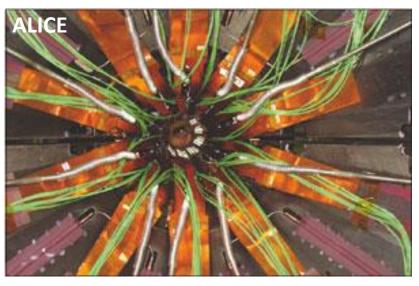

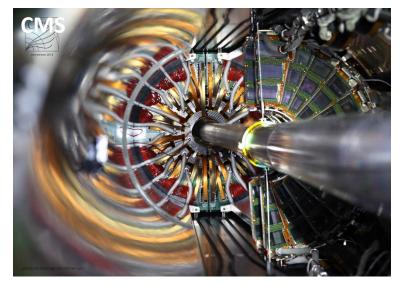

- ATLAS, CMS and ALICE use hybrid pixel detectors near the interaction point

- Complemented by hybrid strip detectors at larger radii

- Largest detector systems ever built in HEP (several m²)

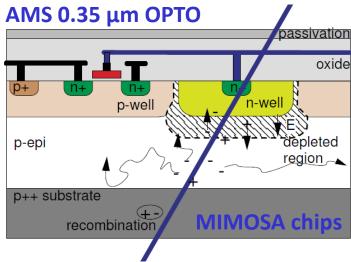

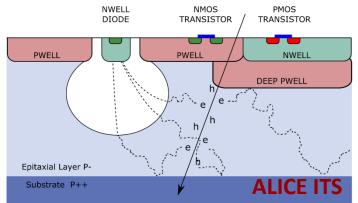

## **Monolithic pixel detectors – MAPS**

- Sensor and readout electronics on single wafer in standard CMOS (low-voltage CMOS)

- Reduced material thickness (50 μm)

- Small pixel size (18 μm x 18 μm)

- In-pixel signal amplification

- More cost effective (~£100k/m²)

- Small bias voltage (V<sub>bias</sub>)

- Slow charge collection by diffusion (2 μs)

- Limited radiation tolerance ( $10^{13}$  1MeV  $n_{eq}$ /cm<sup>2</sup>)

- State-of-the-art for high precision experiments

Pixel = Sensor + simple amplifier

#### TowerJazz 180 nm

Pixel = Sensor + complex electronics

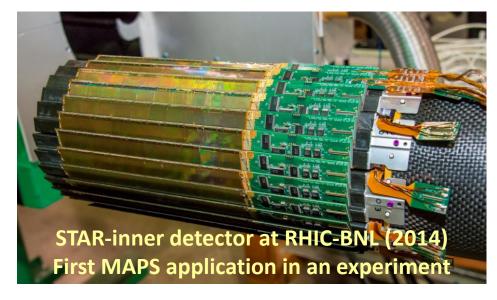

## MAPS in HEP (I)

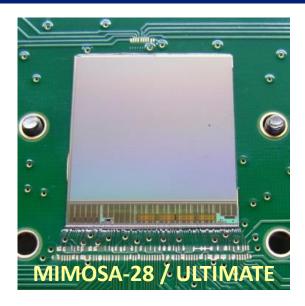

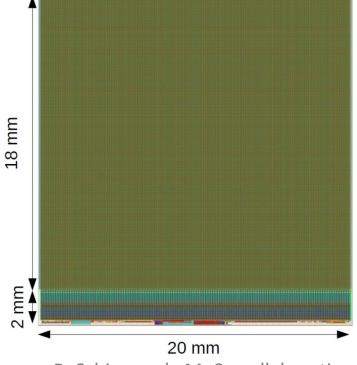

#### MIMOSA-28 / ULTIMATE chip:

Chip size20 mm x 22 mm

Total detector area

0.15 m<sup>2</sup>

Sensor matrix

928 x 960 pixels (~0.9 Mpixels)

– Pixel size 20.7 μm x 20.7 μm

Radiation tolerance 150 krad (TID)

$10^{12}$  1 MeV  $n_{eq}$ /cm<sup>2</sup> (NIEL)

– Process AMS 0.35 μm OPTO

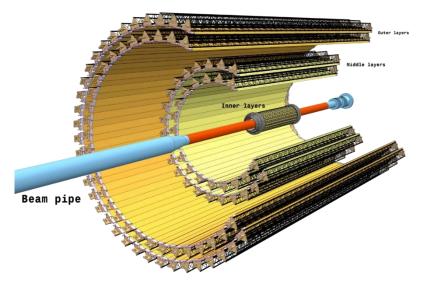

## **MAPS in HEP (II)**

M. Mager, NIM-A: 824 434-438, 2016

**ALPIDE**

**ALICE ITS upgrade (2020)**

#### ALPIDE chip:

Chip size15 mm x 30 mm

Total detector area

12 m<sup>2</sup>

Sensor matrix

512 x 1024 pixels (> 0.5 Mpixels)

– Pixel size 28 μm x 28 μm

Radiation tolerance 700 krad (TID)

$10^{13}$  1 MeV  $n_{eq}$ /cm<sup>2</sup> (NIEL)

ProcessTowerJazz 180 nm

## **Monolithic pixel detectors – Depleted MAPS**

- Sensor and readout electronics on single wafer in standard High Resistivity/High Voltage-CMOS (HR/HV-CMOS)

- Reduced material thickness (50 μm)

- Small pixel size (50 μm x 50 μm)

- In-pixel amplification

- More cost effective (~£100k/m²)

- Larger bias voltage (V<sub>bias</sub>)

- Fast charge collection by drift (15 ns time resolution)

- o Good radiation tolerance ( $10^{15}$  1MeV  $n_{eq}$ /cm<sup>2</sup>)

- One limitation: The chip size is in principle limited to 2 cm x 2 cm, although stitching options are being investigated

- Next generation

## **DMAPS** – History

- HV-CMOS processes originally used for driving automotive or industrial devices

- Attractive for particle physics because

- Silicon bulk biased at high voltage (e.g. -100 V)

- Multiple nested wells to isolate the low-voltage

CMOS readout electronics from the bulk

- N-well

P-substrate

Particle

I. Peric, NIM-A: 582 876-885 (2007)

- Commercially available (i.e. fabrication is low-cost and reliable, there is availability of multiple vendors and large scale production)

- 2007  $\rightarrow$  First publication of a HV-CMOS detector chip (test chip in 0.35  $\mu$ m HV-CMOS process from AMS)

- Small pixel matrix

- Pixels = Sensor + pixel electronics (CSA, discriminator and digital storage)

- Pixel electronics in the deep n-well

- Successful measurements with X-ray and beta radioactive sources

- HV contacts at the top side

## **DMAPS – Commercial vendors (I)**

### GLOBALFOUNDRIES

## **DMAPS – Commercial vendors (II)**

| Foundry → Parameter ↓ | LFOUNDRY | TOWERGLE The Global Specialty Foundry Leader | TSI SEMICONDUCTORS |

|-----------------------|----------|----------------------------------------------|--------------------|

| Feature node          | 150 nm   | 180 nm                                       | 180 nm             |

| HV                    | Yes      | No                                           | Yes                |

| HR                    | Yes      | Yes                                          | Yes                |

| Quadruple well        | Yes      | Yes                                          | No (triple)        |

| Metal layers          | 6        | 6                                            | 6                  |

| Backside processing   | Yes      | Yes                                          | No                 |

| Stitching             | Yes      | Yes                                          | Yes                |

| TSV                   | No       | No                                           | ,                  |

## **DMAPS – Large vs small fill-factor**

| Sensor cross-section → Parameter ↓ | charge signal CMOS electronics  p+ pw nw p+ deep nwell  p - substrate                                                                                                                                                                             | charge signal CMOS electronics  n+ pw nw nw deep pwell p - substrate                                                                                                                                                          |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                               | Large fill-factor (HV/HR-CMOS)                                                                                                                                                                                                                    | Small fill-factor (HR-CMOS)                                                                                                                                                                                                   |

| 1) p/n junction                    | p-substrate/large deep n-well                                                                                                                                                                                                                     | p-substrate/small shallow n-well                                                                                                                                                                                              |

| 2) Substrate biasing               | High voltage                                                                                                                                                                                                                                      | Low voltage                                                                                                                                                                                                                   |

| 3) Substrate resistivity           | < 2-3 kΩ·cm                                                                                                                                                                                                                                       | < 8 kΩ·cm                                                                                                                                                                                                                     |

| 1) + 2) + 3)                       | <ul> <li>No (little) low-field regions</li> <li>Shorter drift distances</li> <li>Higher radiation tolerance</li> <li>Larger sensor capacitance</li> <li>Larger noise &amp; speed/power penalties</li> <li>RO in charge collection well</li> </ul> | <ul> <li>Low-field regions</li> <li>Longer drift distances</li> <li>Lower radiation tolerance</li> <li>Very small sensor capacitance</li> <li>Reduced noise &amp; power</li> <li>RO outside charge collection well</li> </ul> |

| Process                            | AMS/TSI and LFoundry                                                                                                                                                                                                                              | TowerJazz                                                                                                                                                                                                                     |

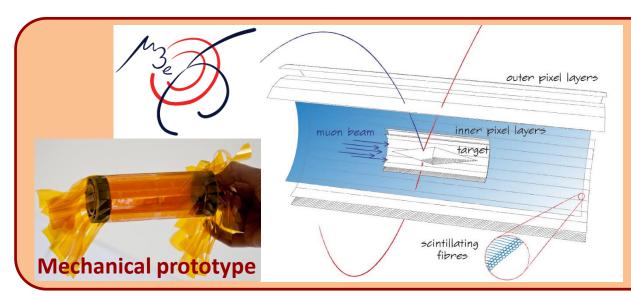

#### **DMAPS in HEP**

- First DMAPS application in an experiment (2019+)

- Requirements:

- Low material 50 μm

- Good time resolution

- < 20 ns (for pixels)

- Fine segmentation 80 μm x 80 μm

## Mu3e – Pixel detector history

| Prototype | Year | Active area (mm²) | Functionality                                           | Main features                                                                               |

|-----------|------|-------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------|

| MuPix1    | 2011 | 1.77              | Sensor + analog RO                                      | First MuPix prototype                                                                       |

| MuPix2    | 2011 | 1.77              | Sensor + analog RO                                      |                                                                                             |

| MuPix3    | 2012 | 9.42              | Sensor + analog/digital RO                              | First digital RO                                                                            |

| MuPix4    | 2013 | 9.42              | Sensor + analog/digital RO                              | Working digital RO and time-<br>stamping                                                    |

| MuPix6    | 2013 | 10.55             | Sensor + analog/digital RO                              |                                                                                             |

| MuPix7    | 2014 | 10.55             | SoC (all relevant features for a fully monolithic chip) | First MuPix prototype with state machine, clock generation and fast serial RO (1.25 Gbit/s) |

| MuPix8    | 2017 | 160               | Large SoC                                               | First large MuPix prototype, with TW correction                                             |

| MuPix9    | 2018 |                   | SoC                                                     | Voltage regulators                                                                          |

| MuPix10   | 2019 |                   | Full size (reticle) SoC                                 | First full size SoC                                                                         |

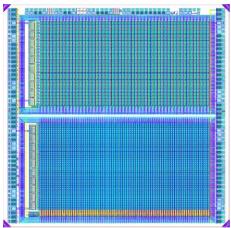

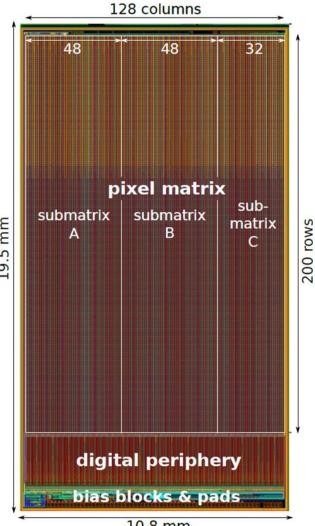

#### Mu3e – MuPix8

#### **MuPix8** - **General design features**

- Engineering run in the **180 nm HV-CMOS process** from ams (aH18)

- Shared with ATLASPix1 (MuPix8 is ~1 cm x 2 cm)

- Fabricated in 2017

- Fabricated using 3 different substrate resistivities

- 10 Ω·cm, 50-100 Ω·cm and 100-400 Ω·cm

#### MuPix8 – Chip details

- Matrix with 128 columns x 200 rows

- 3 matrix partitions (sub-matrices A, B and C)

- 81 μm x 80 μm pixel size

- Analog readout in pixel cell

- Charge sensitive amplifier

- Digital readout in periphery

- Discriminator

- 6-bit ToT

- State machine (continuous readout)

- Time-walk reduction circuitry

- Serial links < 1.6 Gbit/s

- Power consumption ~250 mW/cm<sup>2</sup>

10.8 mm

J. Kroeger, MSc thesis Uni. Heidelberg, 2017

#### Mu3e - MuPix8

Functional block diagram of the chip architecture

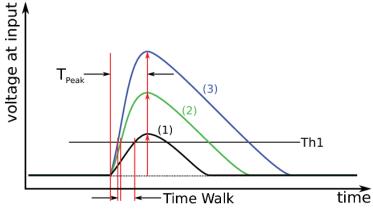

## Mu3e - Time-walk correction

#### **Time-Walk** (TW)

What is it? Variation of the response time of the readout electronics depending on the number of e<sup>-</sup>/h<sup>+</sup> pairs collected by the sensor

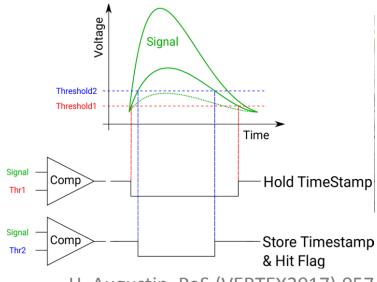

#### TW correction - Two-threshold method

- Two comparators with two threshold voltages:

- VTH1 is very low (close to the noise level)

→ it delivers a time-stamp with small TW

- VTH2 > VHT1 → it confirms that the flagged time-stamp corresponds to a real signal and not to noise

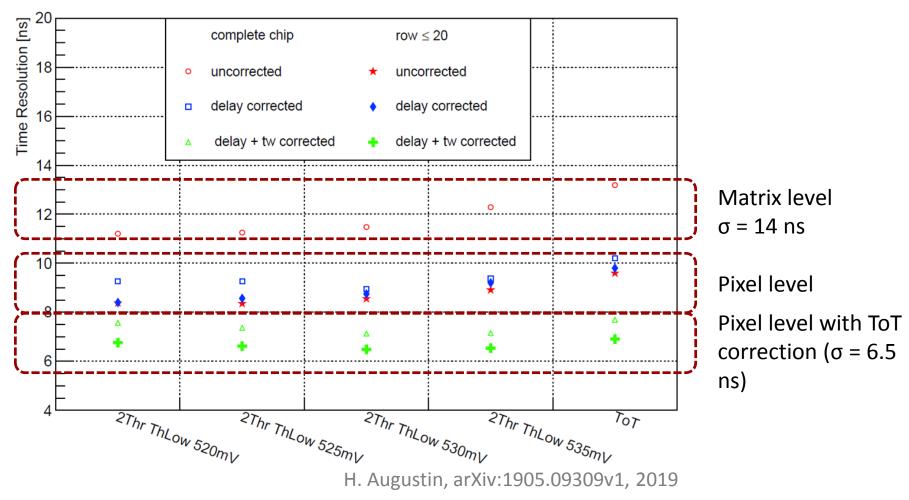

- Measured results show the TW can be reduced to ~6 ns

#### **TW** correction – Other methods

- Increasing the response rate of the amplifier (CACTUS, RD50-MPW2)

- Time-walk compensated comparator (HVStripV1, H35DEMO)

- Sampling method (LF-ATLASPix, CERN-RD50)

R. Schimassek, IEEE NSS/MIC/RTSD, 2016

H. Augustin, PoS (VERTEX2017) 057

#### Mu3e – Time resolution

- Measurement with MuPix8 + scintillator and a Sr90 source

- Time resolution = Time difference between the hit on MuPix8 and scintillator

#### Mu3e – MuPix10

#### MuPix10 - General design features

- Engineering run in the 180 nm HV-CMOS process from TSI

- Submitted in November 2019

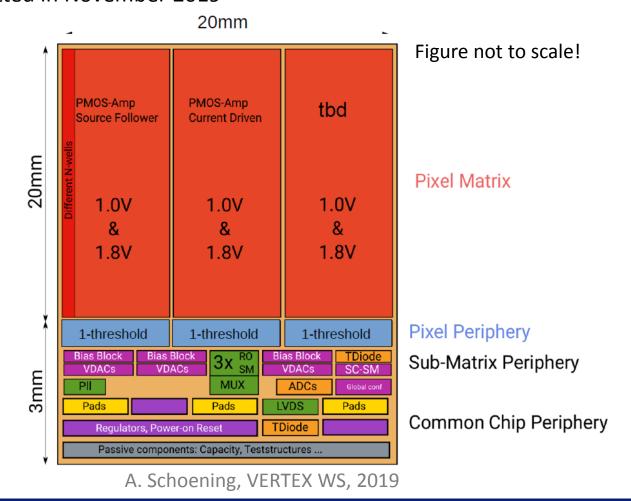

## **ATLAS – Several developments**

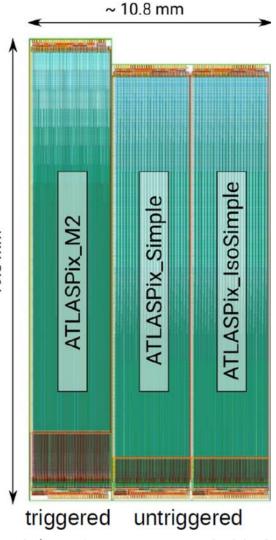

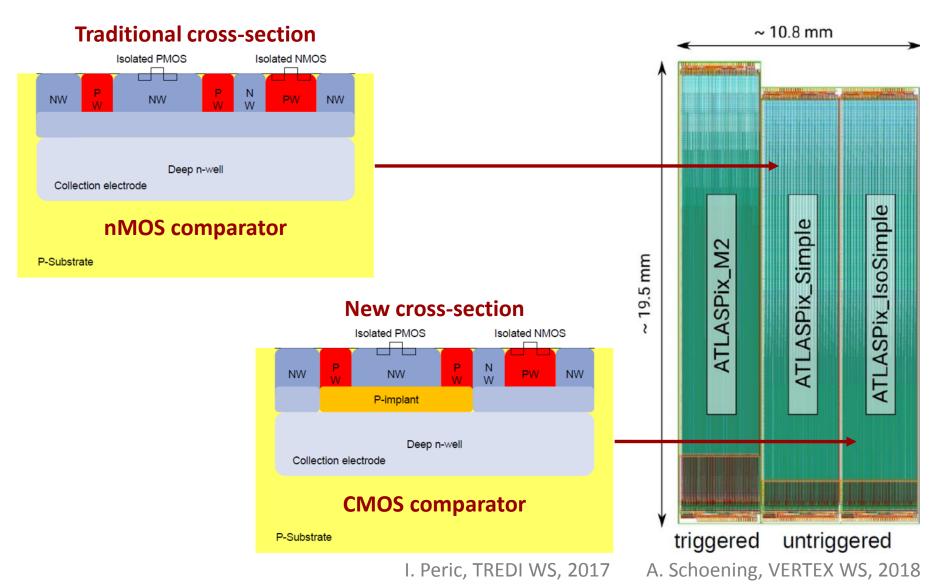

#### ATLAS - ATLASPix1

#### **ATLASPix1** - General design features

- Engineering run in the 180 nm HV-CMOS process from ams (aH18)

- Shared with MuPix8 (ATLASPix1 is ~1 cm x 2 cm)

#### <u>ATLASPix1</u> – <u>Chip details</u> → <u>3 sub-matrices</u>

- ATLASPix\_M2: Triggered readout + no deep p-well

- Matrix with 56 x 320 pixels

- 60 μm x 50 μm pixel size

- Trigger buffers (latency < 25 μs)</li>

- ATLASPix\_Simple: Continuous readout + no deep p-well

- Matrix with 25 x 400 pixels

- 130  $\mu$ m x 40  $\mu$ m pixel size

- $300 \, \text{mW/cm}^2$

- ATLASPix\_IsoSimple: Continuous readout + deep p-well

- Identical to previous matrix, but with deep p-well

- Discriminators in active pixel cell

- 10-bit TS (double check) and 6-bit ToT

- State machine

- Serial link < 1.6 Gbit/s</li>

A. Schoening, VERTEX WS, 2018

#### ATLAS - ATLASPix1

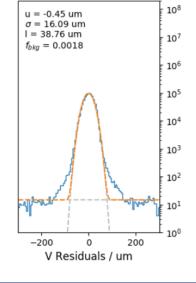

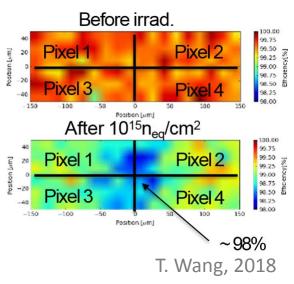

## ATLASPix1 – Efficiency

#### **Test beam campaign** at Fermilab and CERN (**before**/after irradiation)

- 200 Ω·cm

- 60 µm thin

- 60 V bias voltage

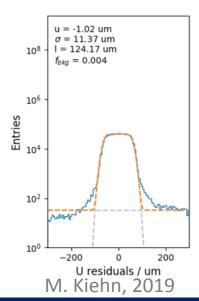

#### **Residuals**

- 60 µm thin

- 65 V bias voltage

- Good alignment

## ATLASPix1 – Efficiency

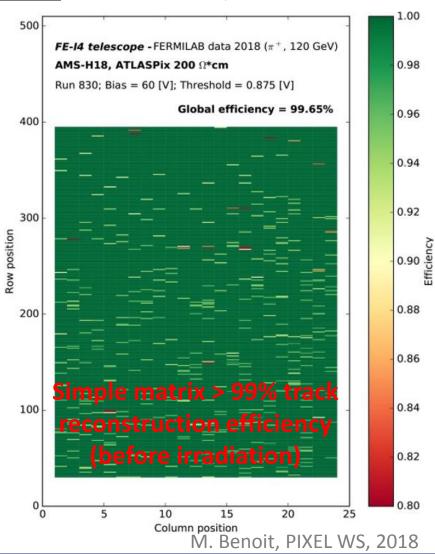

#### **<u>Test beam campaign</u>** at Fermilab and CERN (before/<u>after</u> irradiation)

- 80 Ω·cm samples

- 60 µm thin

- 60 V bias voltage

- 10° C temperature

- Very high efficiency after 10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup> fluences (threshold dependent)

- Low noise (dominated by single pixels)

#### ATLAS – ATLASPix3

#### **ATLASPix3** - General design features

- Engineering run in the 180 nm HV-CMOS process from TSI

- Total chip area is 2 cm x 2 cm

- Fabricated in 2019

#### **ATLASPix3** – Chip details

- Matrix with 132 columns x 372 rows

- 150 μm x 50 μm pixel size

- In-pixel comparator

- Column drain readout with and without trigger

- Trigger latency < 25 μs</li>

- Radiation hard design with SEU tolerant global memory

- Serial powering (only one power supply needed)

- Data interface is very similar to RD53 readout chip (ATLAS)

- Power consumption is ~200 mW/cm2 (with 25 ns time resolution)

- Very initial measured results available

- Expected radiation tolerance is 100 Mrad and 1 x 10<sup>15</sup> 1 MeV n<sub>eq</sub>/cm<sup>2</sup>

R. Schimassek, Mu3e collaboration meeting, 2019

#### ATLAS - LF-MonoPix1

#### <u>LF-MonoPix1</u> - <u>General design features</u>

- Large MPW run in the 150 nm HV-CMOS process from LFoundry

- Total chip area is 10 mm x 9.5 mm

- Fabricated in 2016

- Fabricated using a 2 kΩ·cm substrate resistivity

#### **LF-MonoPix1** – Chip details

- Matrix with 129 columns x 26 rows

- 50 μm x 250 μm pixel size

- In-pixel analog and digital readout electronics

State machine (continuous readout)

#### ATLAS – LF-MonoPix1

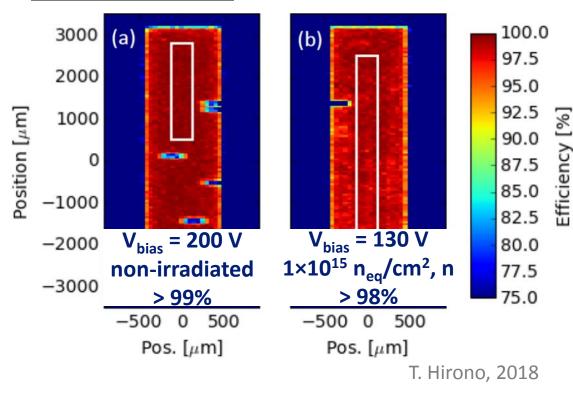

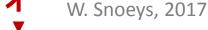

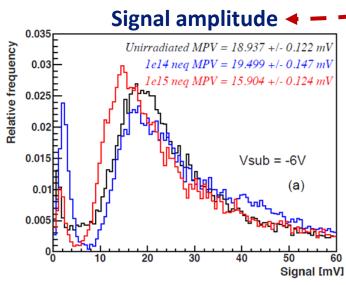

**Test beam campaign** at ELSA with 2.5 GeV electron beam (before/after irradiation)

Most Probable Value (MPV) decreases after 10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup> fluences, but very high efficiency

7 November 2019 - Warwick

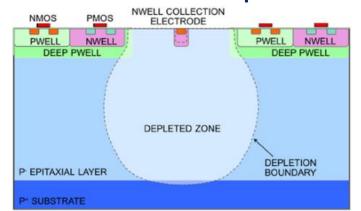

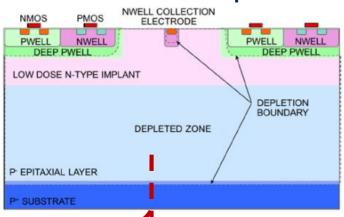

## **ATLAS – Investigator**

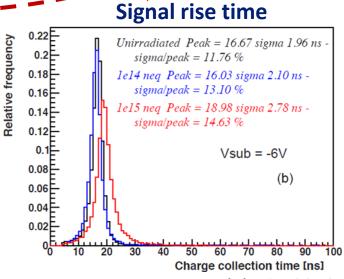

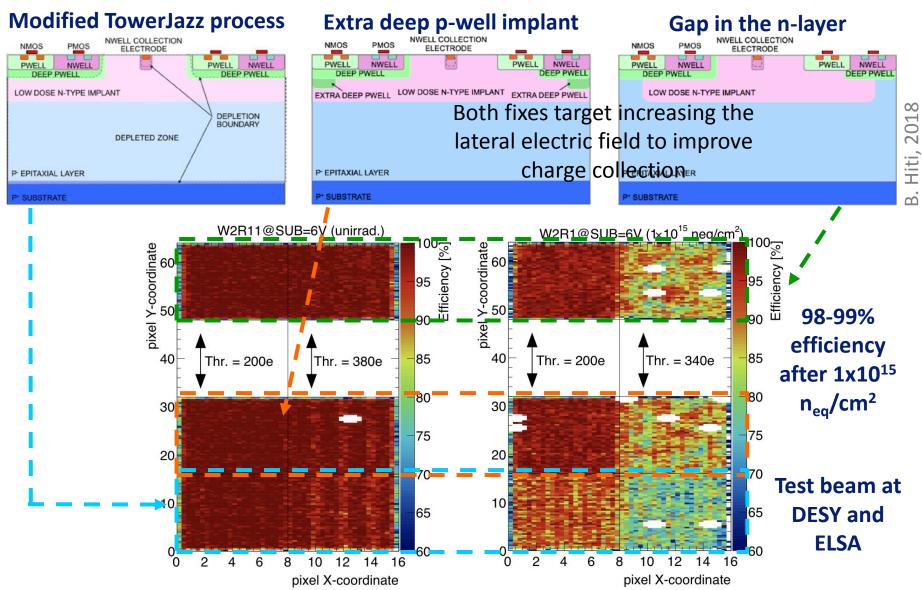

#### **Standard TowerJazz process**

#### **Modified TowerJazz process**

#### **Sr-90** source tests

I. Berdalovic, 2018

#### ATLAS – MiniMALTA

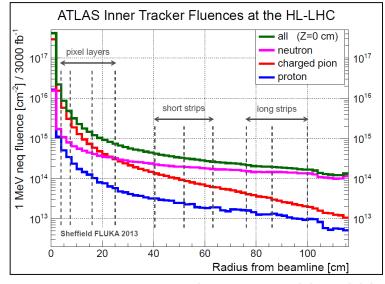

#### **CERN-RD50**

- An international R&D collaboration aimed at developing radiation hard semiconductor devices for high luminosity colliders:

- High Luminosity-LHC (HL-LHC)

- → >  $10^{16}$  1 MeV  $n_{eq}$ /cm<sup>2</sup>

- Future Circular Collider (FCC)

- → >  $7 \times 10^{17}$  1 MeV  $n_{eq}/cm^2$

- Detectors used now at LHC cannot operate after such irradiation. CERN-RD50 is studying new structures:

- N in p sensors

- 3D

- LGAD

- DMAPS

- CERN-RD50 work package to develop and study DMAPS with high priority:

- ASIC design, TCAD simulations, DAQ development and performance evaluation

- ~25 people from ~12 institutions

I. Dawson, ATL-UPGRADEPUB-2014-003, 2014

#### CERN-RD50 - RD50-MPW1

#### **RD50-MPW1 - General design features**

- MPW in the 150 nm HV-CMOS process from LFoundry

- Submitted in November 2017, received in April 2018

- To gain expertise and develop new designs

- Fabricated using 2 different substrate resistivities

- 600  $\Omega$ ·cm and 1.1 k $\Omega$ ·cm

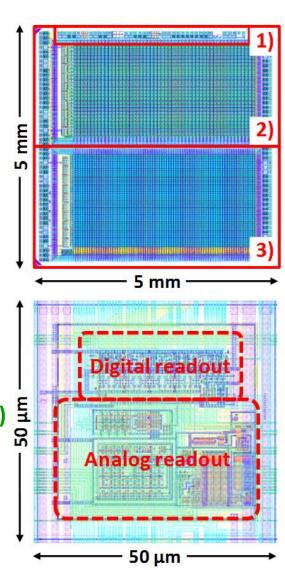

#### RD50-MPW1 - Chip details

- 1) Test structures for eTCT measurements

- 2) Matrix of DMAPS pixels with 16-bit counter

- 26 rows x 52 columns

- 75 μm x 75 μm pixel size

- Aimed at photon counting applications (proof-ofconcept)

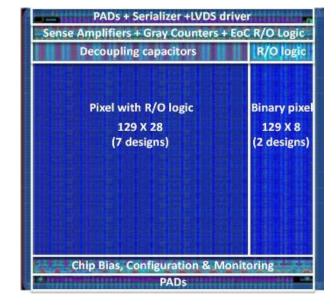

#### 3) Matrix of DMAPS pixels with continuous readout (FE-I3)

- 40 rows x 78 columns

- 50 μm x 50 μm pixel size

- Aimed at particle physics applications

- Analog and digital readout embedded in the sensing area of the pixel

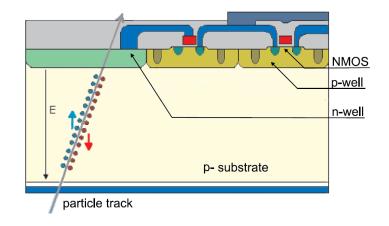

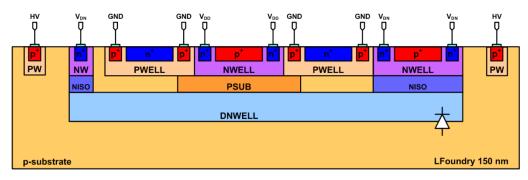

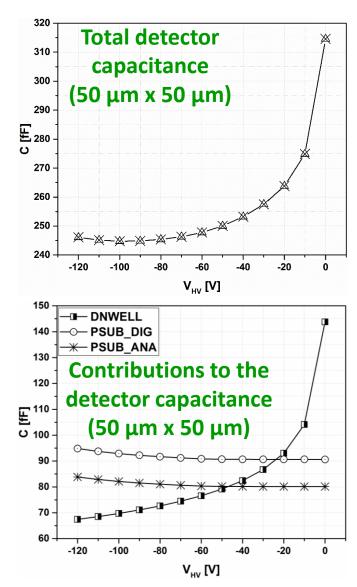

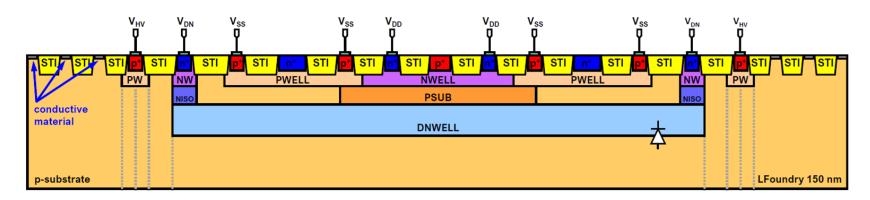

### RD50-MPW1 – Sensor

#### **Sensor cross-section**

- Large fill-factor pixel

- PSUB layer isolates NWELL from DNWELL

- CMOS electronics in pixel area are possible

- Detector capacitance has 2 contributions

- P-substrate/DNWELL

- PSUB/DNWELL

- Total pixel capacitance (50 μm x 50 μm) ~250 fF

- Equivalent Noise Charge (ENC) ~100 120 e<sup>-</sup>

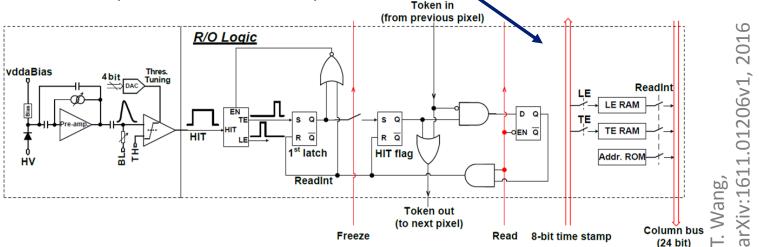

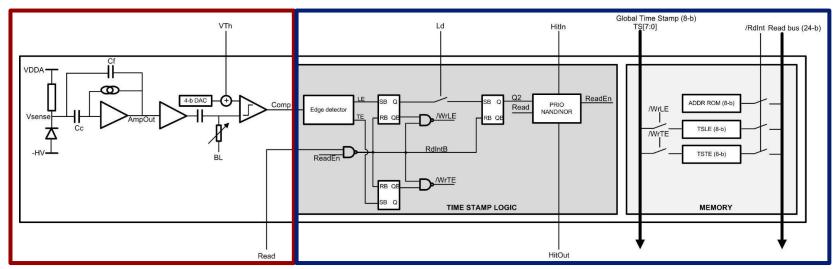

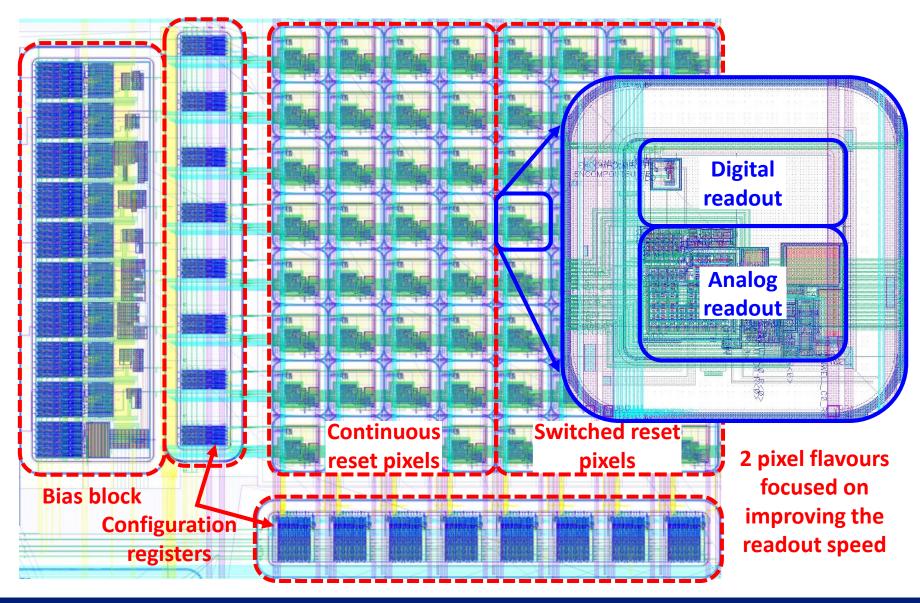

### **RD50-MPW1 – Readout electronics**

#### **Analog readout**

- Sensor biasing circuit, CSA, RC-CR filters and CMOS comparator

- CSA with programmable discharging current

- CMOS comparator with global VTH and local 4-bit DAC for fine tuning

#### **Digital readout**

- Continuous readout (synchronous, triggerless, hit flag + priority encoding)

- Global 8-bit Gray encoded time-stamp (40 MHz)

- For each hit → Leading edge (LE): 8-bit DRAM memory

- → Trailing edge (TE): 8-bit DRAM memory

- → Address (ADDR): 6-bit ROM memory

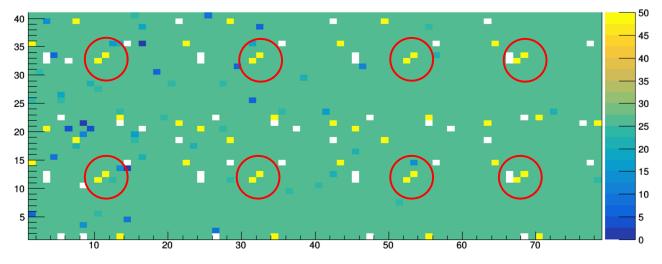

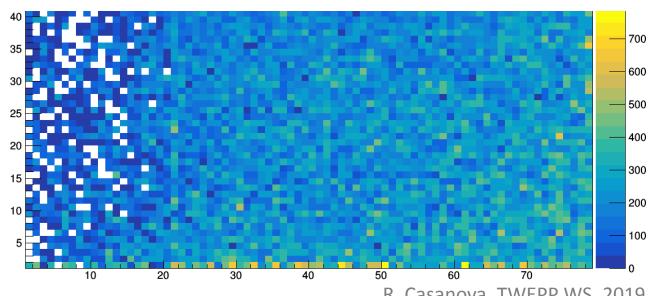

### **RD50-MPW1 – Measured results**

#### **Test pulse injection**

- 25 pulses per pixel

- Some pixels return > 25 hits

- Crosstalk between digital routing lines

#### <u>Sr90</u>

- On matrix centre

- Uniform result expected

- Left / right asymmetry

R. Casanova, TWEPP WS, 2019

### **RD50-MPW1 – Measured results**

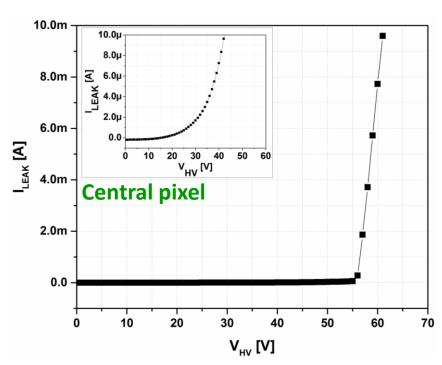

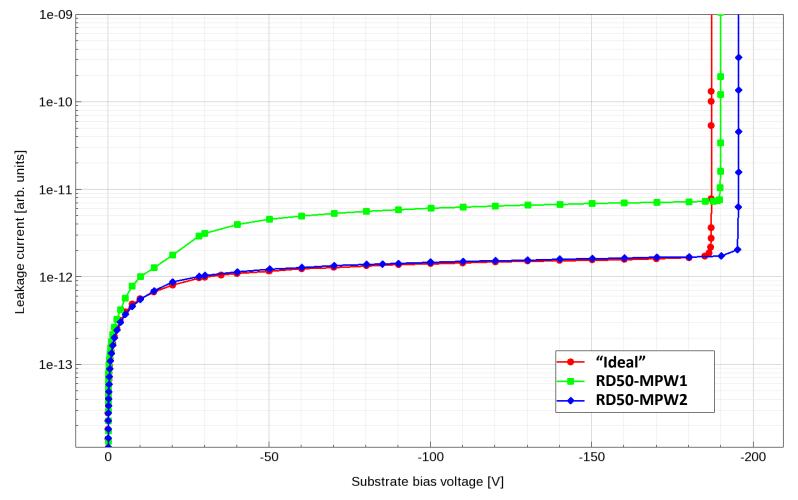

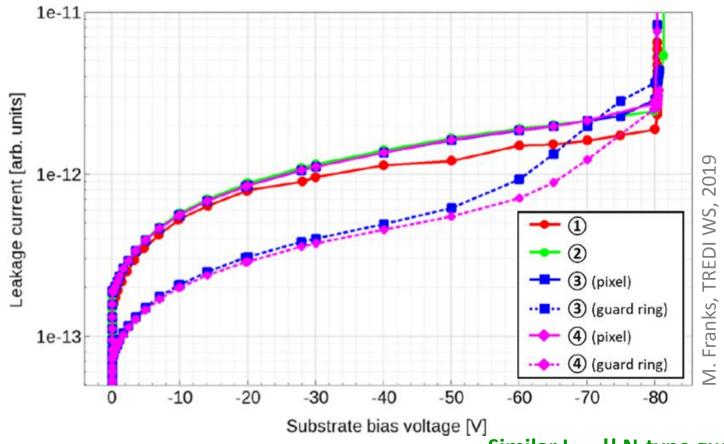

#### I-V curve

- I-V of central pixel of test structure (pixel size is 50 μm x 50 μm)

- Measurement done using a probe station with sensor in complete darkness

- VBD ~ 55-60 V as expected from the design

- ILEAK is too high (μA order well before VBD)

- This issue has been extensively studied: <u>TCAD</u> + <u>support from the foundry</u>

- Methodologies to optimize leakage current in <u>new prototype RD50-MPW2</u>

# **Post-processing – Lessons learned**

- LFoundry adds structures to the design files to prepare them for fabrication.

- These structures involve conductive material.

- We believe these structures contribute quite significantly to the high ILEAK.

- We have minimised the presence of these structures as much as possible.

- Wherever not possible, LFoundry suggested placing these structures inside a PWELL.

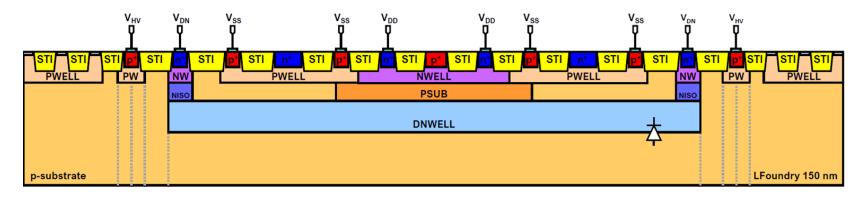

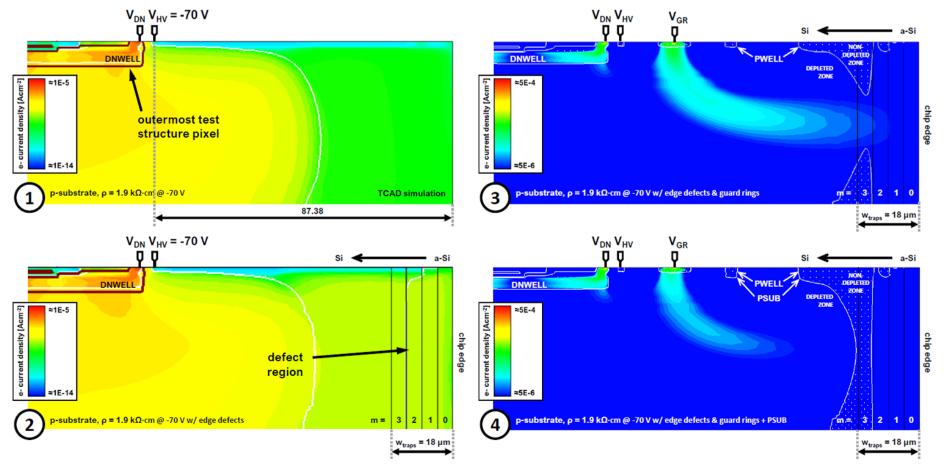

# **Post-processing – TCAD simulations**

### **Electron-current density**

# **Post-processing – TCAD simulations**

- Increase in ILEAK when conductive material is present on the surface (RD50-MPW1).

- ILEAK is reduced when conductive material is placed in PWELL (RD50-MPW2).

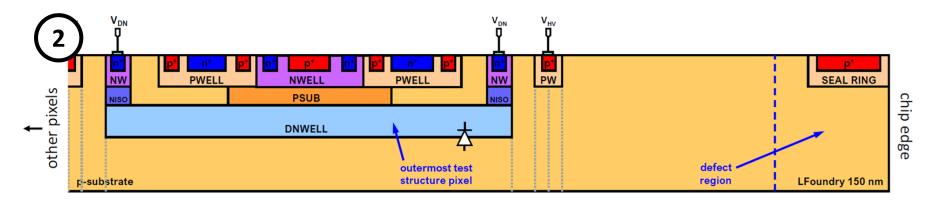

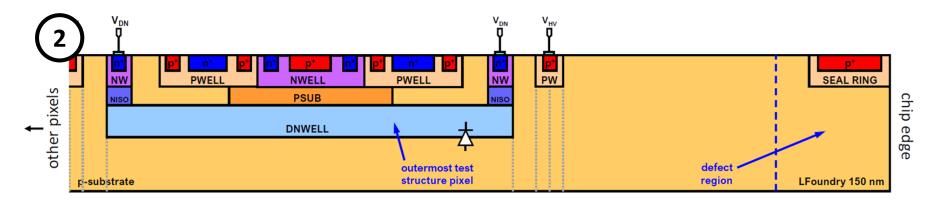

# **Edge defects – Lessons learned**

- Some pixels can be quite close to the edge of the chip

- Defects in silicon lattice due to dicing can become significant

- ILEAK increases when the pixel depletion region is near the defect region

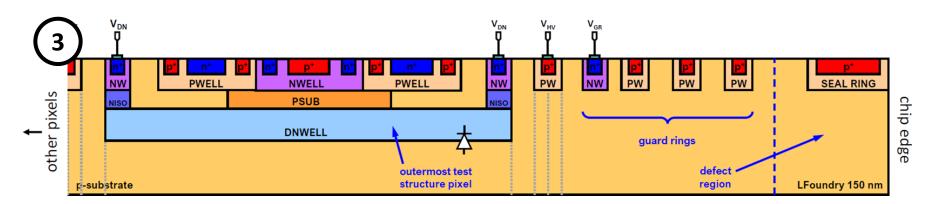

- N-type guard ring added as safeguard to "collect" leakage current

- P-type guard rings added to reduce "lateral" depletion

# **Edge defects – Lessons learned**

- Some pixels can be quite close to the edge of the chip

- Defects in silicon lattice due to dicing can become significant

- ILEAK Increases when the pixel depletion region is near the defect region

- N-type guard ring added as safeguard to "collect" leakage current

- P-type + PSUB guard rings added to further reduce "lateral" depletion

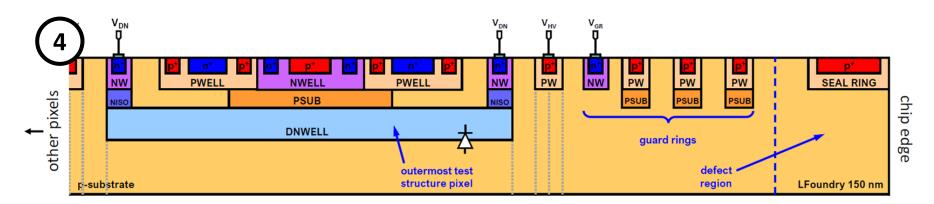

# **Edge defects – TCAD simulations**

- 1) Without defects (ideal case)

- 2) With defects and no guard rings

- 3) With defects, and NWELL and PWELL guard rings

- 4) With defects, and NWELL and PWELL with PSUB guard rings

# **Edge defects – TCAD simulations**

- 1) Without defects (ideal case)

- 2) With defects and no guard rings -

- 3) With defects, and NWELL and PWELL guard rings

- 4) With defects, and NWELL and PWELL with PSUB guard rings

Similar I<sub>LEAK</sub>!! N-type guard ring acts as a diode increasing lateral depletion into defect region.

PSUB reduces I<sub>LFAK</sub> <sup>(2)</sup>

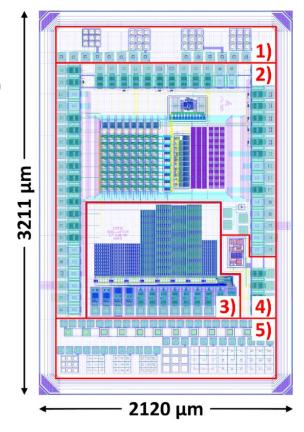

### CERN-RD50 – RD50-MPW2

#### **RD50-MPW2 - General design features**

- MPW in the 150 nm HV-CMOS process from LFoundry

- Submitted in January 2019 (dies expected in December)

- To test methods to minimize the leakage current

- Fabricated using 4 different substrate resistivities

- 10  $\Omega$ ·cm, 100  $\Omega$ ·cm, 1.9 k $\Omega$ ·cm and 3 k $\Omega$ ·cm

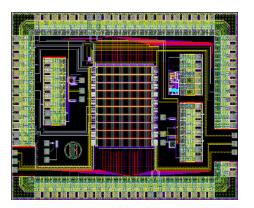

### **RD50-MPW2** – Chip details

- 1) Test structures for eTCT measurements

- 2) Matrix of DMAPS pixels with analog readout only

- 8 rows x 8 columns

- 60 μm x 60 μm pixel size

- Aimed at improving the amplifier response rate

- 3) SEU tolerant memory array

- 4) Bandgap reference voltage

- 5) Test structures with SPADs and DMAPS pixels

- New methodologies to minimize the leakage current

### **CERN-RD50 – RD50-MPW2**

### **Conclusion**

- DMAPS in HR/HV-CMOS processes have huge potential for future particle physics experiments

- Reduced material thickness (50 μm)

- Small pixel size (50 μm x 50 μm)

- More cost effective (~£100k/m²)

- Fast charge collection by drift (15 ns time resolution)

- Good radiation tolerance (10<sup>15</sup> 1MeV n<sub>eq</sub>/cm<sup>2</sup>)

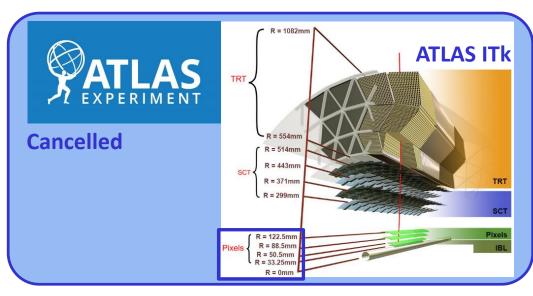

- Quite a few experiments are interested in DMAPS

- Mu3e (first application of DMAPS)

- ATLAS ITk upgrade (cancelled)

- LHCb Mighty Tracker upgrade

- CLIC

- CERN-RD50 (detector R&D)

- Several prototypes and "pre-production" detectors developed for these experiments

- Detector R&D to further develop its performance done within CERN-RD50

# **Back up slides**

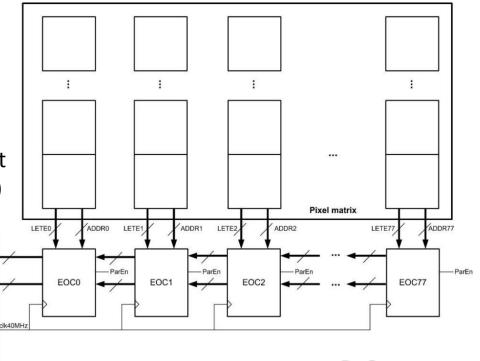

### **RD50-MPW1 – Readout architecture**

- Time-stamp (LE + TE) and pixel address (ADDR) are stored in End

Of Column (EOC) circuit

- If > 1 hits in the same column

- → Pixel with hit flag = '1' and largest address is read out first (hit flag and priority encoding)

LVDS

Shift register with 78 EOC circuits (one EOC per column) @ 40 MHz

SER

SER

R. Casanova, TWEPP 2019

- Continuous readout sequence:

- 1) LE, TE and ADDR of the hit pixel with hit flag = '1' and highest priority stored in EOC (1 clock cycle)

- 2) CU reads sequentially the data stored in each EOC @ 40 MHz (78 clock cycles)

- 3) Serializers send data off-chip @ max. speed of 640 MHz

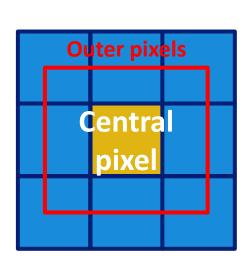

### **RD50-MPW1 – Measured results**

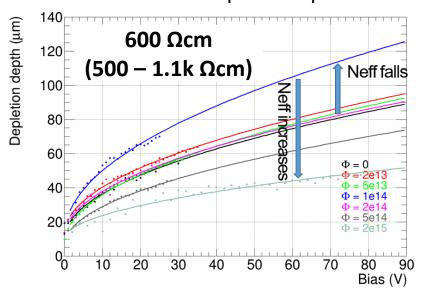

#### eTCT measurements to study sensor depletion region

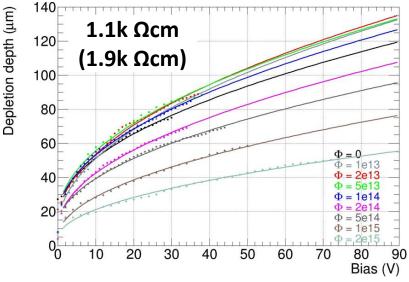

- Samples irradiated at TRIGA reactor in Ljubljana to several different n-fluences ranging from 1E13 to 2E15 n<sub>eq</sub>/cm<sup>2</sup>

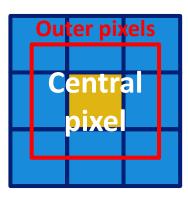

- Test structure

- → 3 x 3 pixels matrix without readout electronics

- → Central pixel to read out

- → Outer pixels connected together

- → Pixel size is 50 µm x 50 µm

Depletion depth changes with irradiation + acceptor removal effects seen

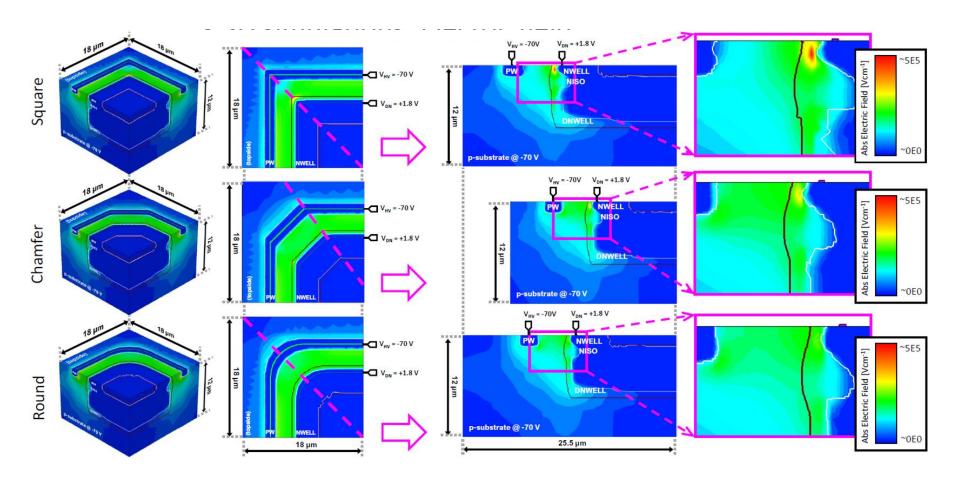

## **CERN-RD50 – TCAD simulations**

### <u>3D simulations</u> – <u>Electric field as a function of corner geometry in pixel</u>