Research

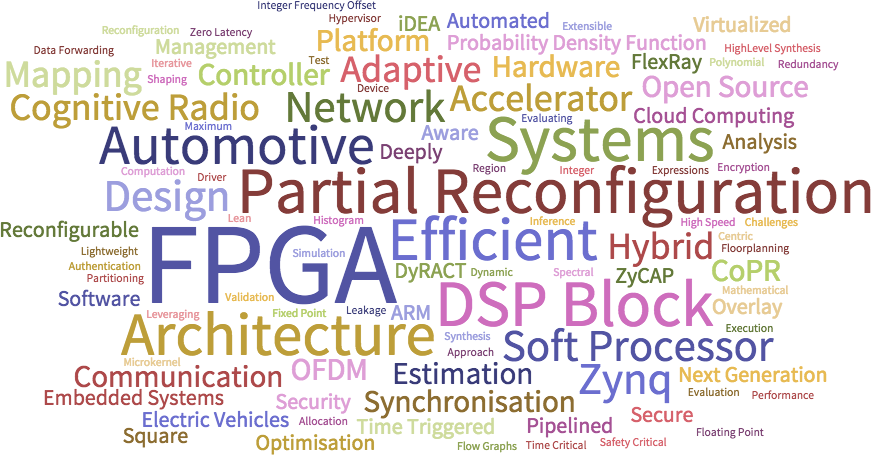

My core interest is in building systems that fuse hardware and software, finding ways to enhance them through novel approaches at that boundary, and applying these concepts in different domains. I have applied such ideas in signal-processing, computer vision, image- and video-processing, communications, and automotive systems. Reconfigurable architectures offer key benefits for developing such systems, and working across abstraction layers allows these to be exploited to a greater extent.

FPGA Partial Reconfiguration

We have a strong body of work on exploiting FPGA partial reconfiguration for enabling adaptive hardware systems. We have built an automated high-level tool-flow, CoPR, that respects vendor tool limitations but abstracts many of the difficult design decisions normally required. We have exploited this in automotive applications and cognitive radios. More recently, we have been generalising this for cognitive systems that require adaptation to environmental conditions.Accelerator Systems

We have been working on methods for integrating accelerator hardware within the context of software systems. At the embedded scale, we have explored the coupling of software with partially reconfigurable hardware, proposing ZyCAP, a custom driver for high speed reconfiguration management on the Xilinx Zynq hybrid FPGA. At the server scale, we have developed DyRACT, allowing reconfigurable accelerators to be managed over PCI Express, with data throughput approaching the limits of the physical interface.Automotive Systems

As cars have become more complex, so too have the networks that interface the rising number of computational components. We have been exploring ways for FPGAs to overcome some of the design and validation challenges in this important area, in collaboration with [TUM CREATE][tumcreate]. We have demonstrated an extensible controller for FlexRay automotive electronic compute units (ECUs), as well as shown how security can be added using a cross-layer approach that incurs negligible overhead.Efficient Architecture Mapping

We have been exploring ways for exploiting the hard blocks in modern FPGAs, specifically, the programmable DSP blocks in Xilinx FPGAs. We proposed the iDEA soft processor that exploits the DSP block's flexible datapath to build a lean processor that can run at over 500MHz on a modern FPGA. We have also proposed new methods for mapping complex functions onto these DSP blocks offering a significant throughput advantage over other methods.Acknowledgements

We would like to acknowledge various entities that support our research. Xilinx has kindly provided a variety of equipment and design tools that are used extensively in our research. We have also received tools donations from Bluespec in the past. We host and manage our code courtesy of GitHub and Bitbucket, which are phenomenal code management services based on Git. (Bitbucket will give you a free unlimited account if you sign up with an educational email address!)

Opportunities

If you are interested in any of the areas I work in, and are considering pursuing a research degree, feel free to send me an email. I am generally interested in students with a background in hardware design with Verilog or VHDL experience. A Masters degree or industrial experience is a significant advantage. Note that I cannot generally offer undergraduate student internships, so please do not email me with such requests.